# A Wideband Low-Noise Downconversion Mixerwith Positive-Negative Feedbacks

#### Hadi Naderian\*

RF Circuit, M.Sc, Electrical Engineering Department, Shahid Bahonar University of Kerman h.naderian@eng.uk.ac.ir

#### Ahmad Hakimi

RF Circuit and Microwave Components, Ph.D, Electrical Engineering Department, Shahid Bahonar University of Kerman Hakimi@uk.ac.ir

Received: 07/Apr/2013 Accepted: 15/Jun/2013

#### **Abstract**

This paper presents a wideband low-noise mixer in CMOS 0.13-um technology that operates between 2–10.5 GHz. The mixer has a Gilbert cell configuration that employs broadband low-noise trans conductors designed using the negative-positive feedback technique used in low-noise amplifier designs. This method allows broadband input matching. The current-bleeding technique is also used so that a high conversion gain can be achieved. Simulation results show excellent noise and gain performance across the frequency span with an average double-sideband noise figure of 2.9 dB and a conversion gain of 15.5 dB. It has a third-order intermodulation intercept point of -8.7 dBm at 5 GHz.

**Keywords:** Current-Bleeding, Feedback, Low-Noise, Noise Cancellation, Wideband.

#### 1. Introduction

Active mixers based on the Gilbert cell configuration often exhibit a large amount of noise. This leads to strict requirements for the noise figure (NF) of the low-noise amplifier (LNA) preceding the mixer such that a particular signal-to-noise ratio can be achieved. This usually requires at least one very low-noise LNA that has enough gain and noise performance to mitigate the noise added by the mixer. Power consumption is also a problem as the LNA NF decreases when larger transistors are used. However, these requirements can be much relaxed or the LNA can be removed if the mixer NF is low enough. The Gilbert cell mixer has been widely used in integrated circuit (IC) design even though it exhibits moderate noise. However, its NF can be drastically reduced by combining the LNA and mixer into a single component. Narrowband low-noise mixers have been proposed in other works [1]-[4], where the transconductors were replaced by inductivedegenerated LNAs.

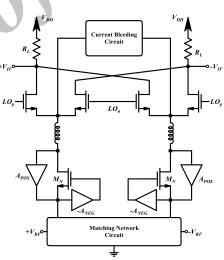

Block diagram of proposed mixer circuit.

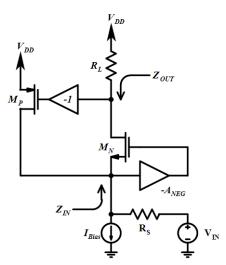

Simplified block diagram of transconductor.

To convert a Gilbert cell into a wideband low-noise mixer, the trans conductors must be wideband in terms of NF, gain, and input matching. Many broadband and UWB LNAs have been proposed [5]–[7]. In [5], an active feedback approach was used to achieve broadband input matching and gain. The circuits in [6] and [7] use filters to achieve broadband input matching and low noise performance. Another broadband LNA design method is the noise-cancelling technique [8], which has been used for mixer in [9].

A common-gate (CG) LNA has been widely investigated because it features superior bandwidth, linearity, stability, and robustness to PVT variations compared to a common-source (CS) topology [10]. In spite of these advantages, the dependence of gain and NF on the restricted transconductance (gm) makes this topology unsuitable for various wireless applications. The input impedance of a CG LNA is simplified as 1/gm, and the noise factor is inversely proportional to gm [11]. In order to achieve high gain and low NF, gm should be increased, which deteriorates the  $50\Omega$  input impedance matching for a conventional CG LNA.

In this paper to achieve high gain and low NF without sacrificing bandwidth, linearity, and power consumption, a differential gm-boosted CG transconductors with a positive-negative feedback technique is proposed. The proposed mixer with output buffers delivers a maximum conversion gain of 15.5 dB, a minimum NF of 2.6 dB, an IIP3 of -8.7 dBm, and 22.44mW power consumption.

# 2. Circuit Description

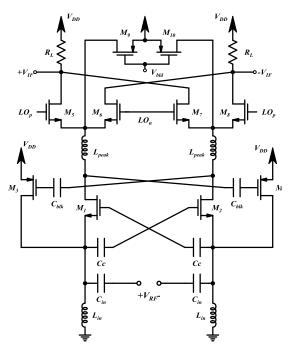

The proposed wideband low-noise mixer block diagram is shown in Figure 1. The mixer based on the Gilbert cell topology with some modifications. The mixer is comprised of four building blocks: positive-negative feedback transconductors, peaking inductors, current bleeding and switching pairs. A detailed design analysis of the positive-negative feedback transconductors block is provided first, followed by a description of each block.

# 2.1 Positive- Negative Feedback Trans conductors

The proposed topology, shown in Figure 2, consists of cross-coupled capacitors in negative and PMOS transistors in positive feedback branches in a differential CG configuration.RL is the mixer load resistor, assuming there is no loss through the switch, and the tail capacitance of the off switch is negligible compared to the load resistor. The differential signals flow to the sources of the NMOS transistors, and are also cross-coupled to the gates of the opposite NMOS transistors through capacitors, which results in a shunt-series negative feedback path [12]-[15]. The outputs of the NMOS transistors are coupled to the sources of the opposite NMOS transistors creating a shunt-shunt positive feedback loop.

The input impedance is obtained as

$$Z_{IN} = \frac{1}{g_{mMn}(1 + A_{NEG})(1 - A_{POS})}.$$

(1)

using input shunt-negative and shunt-positive feedback theory [16]. ANEG, which is approximately given by  $C_C/(C_C+C_{gs})$ , is almost unity. Positive feedback is equivalent to  $g_{mMp}R_L$ , can be varied from 0 to 1 for an arbitrary choice of  $g_{mMp}$  required to achieve an input matching condition. The output impedance is given by  $Z_{OUT} =$

$$\frac{R_{L} \left[ r_{ds} + R_{S} \left\{ 1 + \left( 1 + A_{NEG} \right) g_{m} r_{ds} \right\} \right]}{R_{L} + r_{ds} + R_{S} \left\{ 1 + \left( 1 + A_{NEG} \right) g_{m} r_{ds} \right\} \left( 1 - A_{POS} \right)}$$

(2)

$r_{ds}$  is the output impedance of transconductance transistor. While  $A_{POS}$  is increased, the output impedance, as well as  $g_{mMn}$  for the input matching, can be increased. In this architecture, the voltage gain is given by

$$A_{V} = \frac{g_{m} (1 + A_{NEG})}{2} \times \frac{2}{\pi} \times \frac{R_{L} \left[ r_{ds} + R_{S} \left\{ 1 + (1 + A_{NEG}) g_{m} r_{ds} \right\} \right]}{R_{L} + r_{ds} + R_{S} \left\{ 1 + (1 + A_{NEG}) g_{m} r_{ds} \right\} (1 - A_{POS})}$$

(3)

where  $2/\pi$  is an approximation of switching gain. With the help of gm boosting through the

capacitor cross-coupling (CCC) negative feedback, effective transconductance  $(G_M)$  is the same as the NMOS transconductance itself. As a result, the voltage gain  $(=\!G_M.Z_{OUT})$  can be high with relatively low power consumption through the large  $Z_{OUT}$  and large  $G_M.$

The NF of the circuit can be computed considering thermal channel noise of transconductance transistors and load noise. For high IF thermal noise is dominant, so flicker noise of switching stage was neglected [17]. In this case [18],

$$F = 1 + \frac{\gamma(1 - A_{POS})}{\alpha(1 + A_{NEG})} + g_{mMp}R_S \frac{\gamma}{\alpha} + \frac{R_S}{R_L} (2 - A_{POS})^2$$

$$(4)$$

Where  $\gamma$  is the MOS transistor thermal noise coefficient,  $\alpha$  is defined as the ratio of  $g_{mMn}$  to the zero-bias drain conductance  $g_{d0}$ . The second term represents the channel noise contribution of  $g_{mMn}$ , which can be greatly reduced through  $A_{NEG}$ as well as A<sub>POS</sub>. The channel noise of M<sub>N</sub> flows to the gate and source of an opposite  $M_N$  with the same phase through C<sub>C</sub> and the positive path, respectively. Thus, the combination of positive feedback and the negative feedback loop contributes to channel-noise cancellation. The third and fourth terms show the noise induced by M<sub>P</sub> in the positive feedback path, and the load, respectively. The noise due to M<sub>P</sub> can be decreased by using small g<sub>mMp</sub>, and the load noise is reduced by A<sub>POS</sub>.

# 2.2 Inductive Peaking

The mixer bandwidth can be significantly affected by the large output capacitance from transconductors, as well as from the bleeding circuit and switching pairs. Inductive peaking can be used for bandwidth extension. Series peaking is used in this design and the peaking inductors are placed between the switching pairs and the transconductors, as shown in Figure 1.

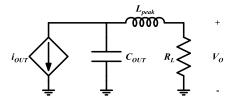

To understand the operation of these inductors, a simplified circuit is shown in Figure 3 when only one of the switches is on. Preceding the mixer core is the transconductors, which can be approximated by a voltage-controlled current source; Cout is the collective output capacitance from the transconductor and the bleeding circuit; R<sub>L</sub> is the mixer load resistor, assuming there is no loss through the switch, and the tail capacitance of the off switch is negligible compared to the load resistor. The basic theory of inductive peaking can be explained with Figure 3 and the step response. Imagine the circuit without the inductor, the rise time at the output is about 2.2RC, if the rise time is defined to be the elapsed time between 10%-90% of the final

output voltage value. To decrease the charge time, i.e., increase the bandwidth, the inductor is used. At t=0, there is a sudden step change in the current source.

Two-pole series peaking network [9].

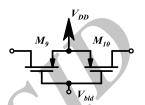

PMOS bleeding circuit.

The high impedance of the inductor decouples the resistor from the capacitor, which means all the current goes into charging the capacitor. Therefore, the rise time decreases, and hence the bandwidth is enhanced.

# 2.3 Switching Pairs and Current Bleeding

In general, increasing the bias current of the RF transconductance stage makes higher gain and better linearity possible, but a larger LO switching current causes voltage headroom issue. Therefore, as shown in Figure 4, the static current bleeding technique is implemented by using two PMOSFETs to reduce the bias current of the LO switches [19].

The gain of the mixer is maximized by fast switching similar to a square wave. The turn-on voltage for the switching pairs is proportional to their overdrive voltage, and it needs to be low to ensure fast switching. By having a lower overdrive voltage, the size of the load resistors can be increased to achieve an even higher gain.

Complete circuit schematic of the proposed mixer.

## 3. Simulation Results

The mixer was designed using TSMC's CMOS 0.13-µm technology. Simulation was run using Advanced Design System (ADS) software. The mixer is designed to operate between 2–10.5 GHz with a local oscillator (LO) power of 0 dBm. Quality factor of peaking inductors and input inductors has been set to 4 and 10, respectively.

For all simulation results, the IF is always kept at a constant 250 MHz, while the RF and LO frequencies are being changed together with the LO being 250 MHz lower than the RF. Two source-follower buffers were used to combine

the differential IF signal into a single-ended output.

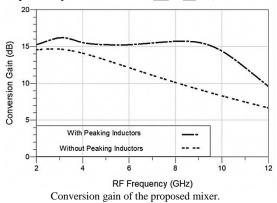

The conversion gain of the mixer is measured across the input frequency ranging from 2 to 10.5 GHz. The input RF power was kept at -40 dBm. Figure 6 shows the conversion gain simulated results. This plot also includes the simulated result without the peaking inductors. The importance of the peaking inductors can be clearly seen in this plot, where there is a much sharper gain roll off compared to the simulated result with peaking.

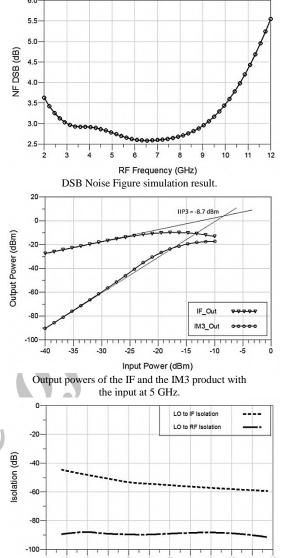

When characterizing the noise performance of a mixer, either the double- or single-sideband

NF can be used [15]. Figure 7 shows the simulated double-sideband NF of the mixer versus input frequency. The circuit has a low and relatively flat NF across bandwidth. The minimum value of NF is 2.6 dB at 6.5 GHz and the maximum is 3.9 dB at 10.5 GHz.

The third-order intermodulation intercept point (IIP3) of the mixers was simulated. To simulate the IIP3, a two-tone signal separated by 1 MHz was used. Shown in Figure 8 is the simulated IF and third-order.

Table I Comparison of Wideband Down-Converters with This Work

| Parameters             | This Work | [20]        | [9]     | [21]         | [22]           | [23]z    |

|------------------------|-----------|-------------|---------|--------------|----------------|----------|

| CMOS Technology        | 0.13 um   | 0.13 um     | 0.13 um | 65 nm        | 90 nm          | 0.18 um  |

| RF Bandwidth (GHz)     | 2 - 10.5  | 3.1 - 10.6  | 1 - 5.5 | 2 - 8        | 0.1 - 3.85     | 0.2 - 13 |

| Conversion Gain (dB)   | 15.5      | 9.8 - 14    | 17.5    | 23 (Voltage) | 12.1           | 9.9      |

| NF DSB (dB)            | 2.9       | 14.5 - 19.6 | 3.9     | 4.5          | 8.4-11.5 (SSB) | 11.7     |

| IIP3 (dBm)             | -8.7      | -11         | +0.84   | -7           | N/A            | -10      |

| LO Power (dBm)         | 0         | 3           | 0       | N/A          | 1              | 5        |

| Voltage Supply (V)     | 1.2       | 1.2         | 1.5     | 1.2          | 1.2            | 0.8      |

| Power Consumption (mW) | 22.44     | 1.85        | 34.5    | 39           | 9.8            | 0.88     |

intermodulation (IM3) output powers with the input RF frequency at 5 GHz. The extrapolated IIP3 was -8.7 dBm.

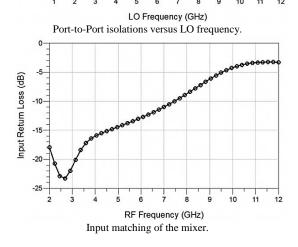

The LO-to-RF port-to-port isolation and LO-to-IF port-to-port isolation were simulated. Since the LO is 250 MHz lower than the RF, the isolation was simulated from 1.75 GHz to 11.75 GHz. Figure 9 shows the simulated mixer ports isolation.

Figure 10 shows the input return loss. The simulation results of conversion gain versus LO input

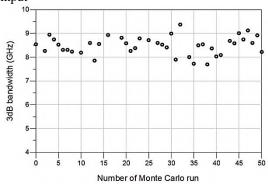

Result of Monte Carlo analysis of the mixer bandwidth.

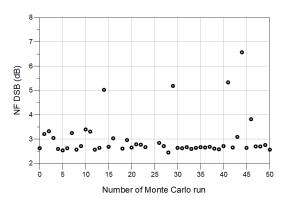

Result of Monte Carlo analysis of the mixer bandwidth

power is shown in Figure 11 which shown that 0 dBm LO power is optimum value for this circuit. The simulation of IF bandwidth is shown in Figure 12 that shows 3-dB bandwidth of conversion gain at the IF port is about 700 MHz. The mixer core draws a total current of 3.54 mA and buffers draws 15.6 mA from a 1.2-V supply, respectively.

The impact of the process and mismatch variations on the mixer frequency response and noise figure has been evaluated by utilizing the well-known Monte-Carlo statistical analysis. Device variations are fluctuations in MOS parameters and include, Effective gate length  $(L_{\rm eff})$ , Threshold voltage  $(V_t)$ , Thickness of the gate oxide  $(T_{\rm ox})$ , and the drain/source region parasitic resistance  $(R_{\rm dsw})$  [24]. The Monte-Carlo simulation of the mixer bandwidth and noise figure is depicted in Figure 13 and Figure 14, respectively. In the noise figure Monte-Carlo analysis has been performed in 6 GHz RF frequency.

Table 1 shows a comparison between this work and recently published broadband down-converters in CMOS. The mixer outperforms others in terms of noise performance while still

having a comparable gain. Their circuit structures are also different. This work and [9] have a current reuse structure, whereas [21] is a LNA Mixer TIA in cascade and [22] is a folded mixer with a folded low-noise transconductors. [23] uses bulk-injection and switched biasing techniques together.

## 4. Conclusion

A double-balanced Gilbert-type mixer based on the positive-negative feedback technique was designed using a 0.13-um CMOS process covering the frequency band between 2 and 10.5 GHz. The noise-cancelling technique allows broadband input matching and noise cancellation at the same time. Together with the currentbleeding technique, a high conversion gain was also achieved. Moreover, parasitic capacitances cancellation was done by adding an extra inductor between switching transconductance stages to obtain better NF and gain performance. The circuit exhibits 2.9 dB average noise figure while the mixer core draws only 3.54 mA form a 1.2-V supply.

### Acknowledgments

This work has been supported under grant UK91-05-07 by the Education & Research Institute for ICT (ERICT) of Iran (Contract number 6987/500). The authors would like to thank Dr. Masoud Movahhedi for his constructive suggestions to improve the manuscript.

#### References

- [1] H. Sjoland, A. Karimi-Sanjaani, and A. Abidi, "A merged CMOS LNA and mixer for a WCDMA receiver," IEEE J. Solid-State Circuits, Vol.38, No.6, pp.1045-1050, Jun. 2003.

- [2] E. Sacchi, I. Bietti, S. Erba, L. Tee, P. Vilmercati, and R. Castello, "A 15mW, 70 kHz 1/f corner direct conversion CMOS receiver," in Proc. IEEE Custom Integr. Circuits Conf., Sep. 2003, pp.459-462.

- [3] T.-A. Phan, C.-W. Kim, M.-S. Kang, S.-G. Lee, and C.-D. Su, "A high performance CMOS direct down conversion mixer for UWB system," IEICE Trans. Electron., Vol. E88-C, No.12, pp.2316–2321, Dec. 2005.

- [4] A. Liscidini, A. Mazzanti, R. Tonietto, L. Vandi, P. Andreani, and R.Castello, "Single-stage lowpower quadrature RF receiver front-end: The LMV cell," IEEE J. Solid-State Circuits, Vol.41, No.12, pp.2832–2841, Dec. 2006.

- [5] S. Andersson, C. Svenson, and O. Drugge, "Wideband LNA for a multistandard wireless receiver in 0.18 m CMOS," in Proc. 29th Eur. Solid-State Circuits Conf., Sep. 2003, pp.655–658.

- [6] A. Bevilacqua and A. Niknejad, "An ultrawideband CMOS low-noise amplifier for 3.1–10.6-GHz wireless receivers," IEEE J. Solid-State Circuits, Vol.39, No.12, pp.2259-2268, Dec. 2004.

- [7] A. Bevilacqua, C. Sandner, A. Gerosa, and A. Neviani, "A fully integrated differential CMOS LNA for 3-5-GHz ultrawideband wireless receivers," IEEE Microw. Wireless Compon. Lett., Vol.16, No.3, pp.134-136, Mar. 2006.

- [8] F. Bruccoleri, E. Klumperink, and B. Nauta, "Wide-band CMOS lownoise amplifier exploiting thermal noise canceling," IEEE J. Solid-State Circuits, Vol.39, No.2, pp.275-282, Feb. 2004.

- [9] Stanley S. K. Ho, and Carlos E. Saavedra, "A CMOS Broadband Low-Noise Mixer With Noise Cancellation," IEEE Transactions On Microwave Theory And Techniques, Vol.58, No.5, May 2010.

- [10] H. Darabi and A. A. Abidi, "A 4.5mW 900MHz CMOS Receiver for Wireless Paging,"IEEE J. Solid-State Circuits, Vol.35, No.8, pp.1085-1096, Aug. 2000.

- [11] X. Guan, A. Hajimiri, "A 24GHz CMOS Front-End," IEEE J. Solid-State Circuits, Vol.39, issue 2, pp.368-373, Feb. 2004.

- [12] S. Woo, W. Kim, C. Lee, K. Lim and J. Laskar "A 3.6 mW differential common-gate CMOS LNA with positive–negative feedback", IEEE Int. Solid-State Circuits Conf. Tech. Dig., pp.218-219, 2009.

- [13] Naderian, H.; Hakimi, A.; Movahhedi, M.; "A wideband low-noise down conversion mixer with positive-negative feedbacks," Electrical Engineering (ICEE), 2012 20th Iranian Conference on, Vol., No., pp.206-210, 15-17 May 2012.

- [14] Sanghyun Woo; Woonyun Kim; Chang-Ho Lee; Hyoungsoo Kim; Laskar, J.; "A Wideband Low-Power CMOS LNA With Positive—Negative Feedback for Noise, Gain, and Linearity Optimization," Microwave Theory and Techniques, IEEE Transactions on, Vol.60, No.10, pp.3169-3178, Oct. 2012.

- [15] W. Zhuo, X. Li, Shekhar, S. H. K. Embabi, J. P. de Gyvez, D. J.Allstot, and E. Sanchez-Sinencio, "A Capacitor Cross-Coupled Common-Gate Low-Noise Amplifier", IEEE Journal of Transactions on Circuits and Systems, Dec. 2005, No.12, pp.875-879.

- [16] Paul R. Gray, Paul J. Hurst, Stephen H. Lewis, Robert G. Meyer, "Analysis and Design of Analog Integrated Circuits", 5th Edition, John Wiley & Sons, May 2009.

- [17] Wei Cheng; Annema, A.J.; Croon, J.A.; Nauta, B.; "Noise and Nonlinearity Modeling of Active Mixers for Fast and Accurate Estimation," Circuits and Systems I: Regular Papers, IEEE Transactions on, Vol.58, No.2, pp.276-289, Feb. 2011.

- [18] A. Liscidini, et al., "Analysis and Design of Configurable LNAs in Feedback Common-Gate Topologies," IEEE Trans. Circuits and Systems-II, Vol.55, No.8, pp.733-737, Aug.2008.

- [19] H. Darabi and J. Chiu, "A noise cancellation technique in active-RF CMOS mixers," in Int. Solid-State Circuits Conf., 2005, pp.544-545, Session 29.

- [20] S. Jeong-Bae, K. Jong-Ha, S. Hyuk, and Y. Tae-Yeoul, "A Low-Power and High-Gain Mixer for UWB Systems," Microwave and Wireless Components Letters, IEEE, Vol.18, pp.803-805, 2008.

- [21] S. Lee, J. Bergervoet, K. Harish, D. Leenaerts, R. Roovers, R. van de Beek, and G. van der Weide, "A broadband receive chain in 65 nm CMOS," in IEEE Int. Solid-State Circuits Conf. Tech. Dig., Feb. 2007, pp.418–612.

- [22] A. Amer, E. Hegazi, and H. F. Ragaie, "A 90-nm wideband merged CMOS LNA and mixer exploiting noise cancellation," IEEE J. Solid-State Circuits, Vol.42, No.2, pp.323-328, Feb. 2007.

- [23] Myoung-Gyun Kim; Hee-Woo An; Yun-Mo Kang; Ji-Young Lee; Tae-Yeoul Yun, "A Low-Voltage, Low-Power, and Low-Noise UWB Mixer Using Bulk-Injection and Switched Biasing Techniques," Microwave Theory and Techniques, IEEE Transactions on , Vol.60, No.8, pp.2486,2493, Aug. 2012.

- [24] Venkatraman, V.; Burleson, W., "Impact of process variations on multi-level signaling for on-chip interconnects," VLSI Design, 2005. 18th International Conference on, Vol., No., pp.362,367, 3-7 Jan. 2005.