### International Journal of Engineering

Journal Homepage: www.ije.ir

# Design and Implementation of a Constant Frequency Sliding Mode Controller for a Luo Converter

### A. Goudarzian\*, H. Nasiri, N. Abjadi

Faculity of Engineering, Shahrekord Univercity, Shahrekord, Iran

### PAPER INFO

ABSTRACT

Paper history: Received 19 May 2015 Received in revised form 08 September 2015 Accepted 26 January 2016

Keywords: POESLL Converter Constant Frequency Sliding Mode Controller Laboratory Prototype In this study, a robust controller for voltage regulation of a POESLL converter operated in continuous conduction mode is presented. The POESLL converter is a DC/DC converter with a high voltage gain. DC/DC converters are used in telecommunication systems, power sources and industrial applications. Owing to the switching operation, the structure of the POESLL converter is non-linear. In addition, because of the load and input voltage variations, the structure of the POESLL converter is time-varying. In order to regulate the output voltage of the POESLL converter, a non-linear controller is required. The proposed controller is developed based on constant frequency sliding mode method. The sliding mode controllers can cope with the non-linear and time-varying structure of the DC/DC converters. The performance of the proposed controller is studied in PSIM software. A laboratory model of the proposed controller has been implemented. In this paper, design, simulations and experimental results are presented to show the effective performance of the proposed controller for voltage regulation of the POESLL converter.

doi: 10.5829/idosi.ije.2016.29.02b.09

### **1. INTRODUCTION**

Nowadays, DC/DC converters are widely used in industrial applications [1, 2]. Theoretically, the conventional DC/DC converters such as boost, cuk, buck-boost, zeta and sepic can be used to increase the output voltage. However, in practical conditions, the voltage gain of the DC/DC converters is limited because of the parametric effects and inductor coil saturation. In addition, high increment in the output voltage increases switching losses.

The super lift (SL) method has been widely used in the design of DC/DC converters [3]. In this method, voltage gain of DC/DC converter increases in geometric progression. The positive output elementary super lift Luo (POESLL) converter has been designed based on super lift method. The POESLL converter is an attractive topology with a high voltage gain. In the same operating conditions, the inductor average current of the POESLL converter is less than the inductor average current of other conventional DC/DC converters. The

\*Corresponding Author's Email: <u>alireza.g@stu.sku.ac.ir</u> (A. Goudarzian)

inductor current is limited because of the inductor coil saturation problem. Therefore, the POESLL converter is a suitable candidate for power systems. The structure of the POESLL converter is non-linear and time-varying. To overcome these problems, a non-linear controller with robust performance is needed.

The signal flow graph (SFG) method has been widely used for modeling DC/DC converters [4, 5]. The design based on SFG method is simple; however, some dynamic characteristics are averaged out in the model of DC/DC converter. It attenuates the performance of the converter against parametric variations. The small signal sliding mode method for DC/DC converters has been introduced in [6]; however, this controller is designed in a specific operating point.

Design and implementation of proportional integral controllers and proportional integral divertive controllers have been reported in [7-10]. These controllers are sensitive against input voltage and load variations. The non-linear controllers possess many advantages compared with linear controllers. These are appropriate for large signal models. Based on such models, many non-linear techniques have been presented, for example, feedback linearization [11] and

Please cite this article as: A. Goudarzian, H. Nasiri, N. Abjadi, Design and Implementation of a Constant Frequency Sliding Mode Controller for a Luo Converter, International Journal of Engineering (IJE), TRANSACTIONS B: Applications Vol. 29, No. 2, (February 2016) 202-210

backstepping methods [12]; However, implementation of these controllers may be expensive and complicated. The sliding mode controller (SMC) is a type of nonlinear controller. It is used for both linear and non-linear systems [13]. This control ensures stability of the POESLL converter in a wide range of operating conditions. In addition, the implementation of SMC is simple compared with other non-linear controllers. It is shown that the SMC is a possible solution for enhancing the performance of DC/DC converters [14, 15].

The traditional SMCs are developed by applying the hysteresis method (HM) [16-18]. In [19], a HM based SMC has been presented for output voltage regulation of the POESLL converter. In [20], current control for paralleled POESLL converters using HM based SMC has been introduced. In [21], a fuzzy logic controller-HM based SMC has been reported for DC/DC converters. These studies have shown the robust performance of the SMC; however, the HM based SMC has a major disadvantage. In this method, the switching frequency of DC/DC converter is variable, because of the hysteresis modulation. The variable frequency will result in noise and electromagnetic interference problems, inductor losses and large switching losses. In addition, it makes the design of the input and output filters more complicated. The constant frequency sliding mode method has been presented [22-24], which has these major disadvantages: difficulty in design and implementation and requiring more sensors and more calculations.

In this paper, design and implementation of a constant frequency SMC for a POESLL converter operated in continuous conduction mode are presented. This method is developed based on the equivalent control approach. In this method, an appropriate sliding surface S is defined. Then, an equivalent control law  $u_{eq}$ is derived in terms of the state variables of the converter by solving  $\dot{S} = 0$ . Consequently, the defined sliding surface is indirectly enforced to reach the origin (S=0). In practice, in the implementation of the constant frequency sliding mode controller, the control law u<sub>eq</sub> is constructed using a pulse width modulator. In this paper, the model of POESLL converter is derived. Then, the constant frequency SMC is designed. The performance of the proposed controller for POESLL converter is studied in different operating conditions. The analogue implementation of the proposed system is a useful contribution for researchers. The design of the constant frequency sliding mode controller is done using the reduced order equations of the POESLL converter. The advantages of this method are: less computations and less number of sensors [25].

This paper is organized as follows: In section 2, the average model of POESLL converter is derived and the performance of the converter is studied. In section 3, design of the proposed controller is done. The simulations and experimental results of the proposed system at various operating points are discussed in section 4. Finally, the conclusions are listed in section 5.

## 2. MODEL OF A POESLL CONVERTER IN CONTINUOUS CONDUCTION MODE

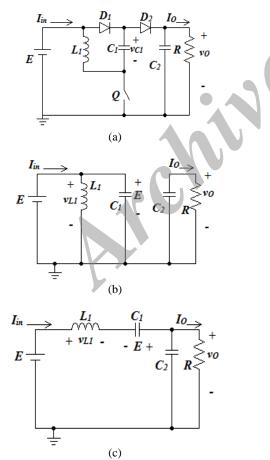

The diagram of the POESLL converter is shown in Figure 1(a). The output voltage increment can be performed by controlling the duty cycle of the switch. The POESLL converter is constituted of two diodes  $D_1$ ,  $D_2$ , two capacitors  $C_1$ ,  $C_2$ , inductor L and power switch Q. In Figure 1(a), R and E are load and input voltage, respectively.  $i_L$  is inductor current,  $v_{C1}$  capacitor ( $C_1$ ) voltage and  $v_0$  is output voltage. It is supposed that the POESLL converter operates in continuous conduction mode and components of the converter are ideal. The circuit operation of the POESLL converter is studied in two conditions: The switch-ON condition and the switch-OFF condition. Figures 1(b) and (c) show these two conditions.

In switch-ON state, diode  $D_1$  and switch conduct. Diode  $D_2$  is OFF. The inductor current  $(i_L)$  is charged with slope E/L and capacitor  $C_1$  is charged by input voltage. The load energy is provided by output capacitor.

In switch-OFF state, diode  $D_1$  and switch are OFF and diode  $D_2$  conducts. The inductor current is discharged with slope (2E-v<sub>0</sub>)/L. In this state, inductor L and capacitor  $C_1$  provide the output energy. The capacitor voltage  $v_{C1}$  is fixed with the assumption that the capacitor value  $C_1$  is large enough. Therefore, the following relation is obtained for all times:

$$v_{\rm C1}(t) = \mathbf{E} \tag{1}$$

Using (1), the averaged model of the POESLL converter is expressed as (2).

$$\begin{cases} L\frac{di_L}{dt} = E + 1 - u \quad E - v_o \\ C_2 \frac{dv_o}{dt} = 1 - u \quad i_L - Gv_o \end{cases}$$

(2)

where  $u \epsilon (0, 1)$

### 3. COMPARISION BETWEEN THE POESLL CONVERTERAND OTHER CONVENTIONAL CONVERTERS

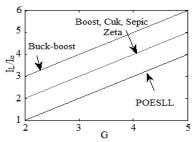

In this section, the inductor average current of the POESLL converter is compared with the inductor average current of other conventional converters such as boost, cuk, buck-boost, sepic and zeta. This comparison is useful, because of the inductor losses problem. The inductor average current of the POESLL is obtained as:

$$I_L = \frac{I_{in}}{2-u} \tag{3}$$

In ideal conditions,  $P_0=P_{in}$  then the relation between inductor average current and output average current is:

$$P_{in} = P_o \rightarrow EI_{in} = V_o I_o \rightarrow \frac{I_L}{I_o} = \frac{V_o}{E \ 2 - u} = G - 1 \tag{4}$$

where  $G=V_O/E$  in steady state region.

The relation between inductor average current and output average current for other conventional DC/DC converters is obtained as (5).

$$\begin{vmatrix} I_{L} \\ I_{O} \end{vmatrix} = G \qquad For \ Boost, Cuk, Sepic, Zeta \\ \begin{vmatrix} I_{L} \\ I_{O} \end{vmatrix} = G + 1 \qquad For \ Buck-boost \qquad (5)$$

A plot of  $I_L/I_O$  versus G is shown in Figure 2. It is clear that the inductor average current of the POESLL converter is less than that of other converters.

**Figure 1.** Diagram of the POESLL converter (a) Topology of the POESLL converter (b) POESLL converter in switch-ON condition (c) POESLL converter in switch-OFF condition

Figure 2. Plot of I<sub>L</sub>/I<sub>O</sub> versus G for DC/DC converters

### 4. DESIGN OF CONSTANT FREQUENCY SMC FOR THE POESLL

The SMC is flexible in design and simple in implementation. All the state variables of the converter can be sensed to generate the sliding surface, which enhance the performance of the SMC; however, this method makes the design of the controller more complicated [22-24]. It is worthwhile to note that complexity in the design of the sliding mode controller can be reduced by selecting a proper sliding surface. In this paper, the reduced order model of the converter is used to design the SMC. Therefore, only  $i_L$  and  $v_O$  are sensed to generate sliding surface. These variables are sufficient to regulate the output voltage of the converter. Here, the sliding surface of the POESLL converter is expressed as:

$$S = ai_{L} + bv_{O} + c\int \beta v_{O} - V_{d}$$

(6)

where a, b, c are controller parameters,  $V_d$  is the output voltage reference and  $\beta$  is a positive constant. In steady state region,  $\beta V_0 = V_d$ . The presence of integral term of the output voltage reduces the output voltage error in steady state region [7]. Using Equations (2) and (6), the derivative of the sliding surface is obtained as:

$$\dot{S} = \frac{aE}{L} + \frac{a}{L} + \frac{a}{L} + \frac{bi_{C2}}{L} + c \beta v_o - V_d$$

(7)

The equivalent control law is obtained by solving  $\dot{S} = 0$ . It can be written as:

$$u_{eq} = \frac{k_1 \ 2E - v_o \ + k_2 i_{C2} + k_3 \ \beta v_o - V_d}{k_1 \ E - v_o}$$

(8)

where:

$$k_1 = \frac{a}{L}, k_2 = \frac{b}{C_2}, k_3 = c \tag{9}$$

It can be seen that the output voltage and output capacitor current appear in equivalent control law  $u_{eq}$ . Therefore, these variables must be sensed to generate the equivalent control law. According to sliding mode theory, three conditions must be checked to ensure the

stability of the closed loop system: eexistence condition, reaching condition, stability condition {Tan, 2007 #23;Tan, 2008 #25;He, 2010 #26}.

**4. 1. Existence Condition** This condition ensures the existence of the sliding mode operation. The existence condition determines the acceptable range of the controller coefficients. This condition guarantees that all phase trajectories of the controller in the phase portrait are directed toward the sliding surface. It is expressed as Equation (10).

$$\begin{cases} \lim_{s \to 0^{\circ}} \dot{S} > 0 \\ \lim_{s \to 0^{\circ}} \dot{S} < 0 \\ \end{cases}$$

(10)

when  $\dot{S} > 0$ , S<0, u=1 then:

$$\dot{S} = \frac{aE}{L} + \frac{bi_{C2}}{C_2} + c \ \beta v_0 - V_d > 0$$

(11)

when  $\dot{S} < 0$ , S>, u=0 then:

$$\dot{S} = \frac{aE}{L} + \frac{a \ E - v_o}{L} + \frac{bi_{C2}}{C_2} + c \ \beta v_o - V_d < 0$$

(12)

The existence condition is expressed as:

$$\begin{cases}

\frac{2aE_{\max}}{L} - \frac{av_{omax}}{L} + \frac{bi_{C2\max}}{C_2} + c \quad \beta v_{omax} - V_d < 0 \\

\frac{aE_{\min}}{L} + \frac{bi_{C2\min}}{C_2} + c \quad \beta v_{omin} - V_d > 0

\end{cases}$$

(13)

### 4. 2. Reaching Condition

guarantees that all the state variables of the system reach the origin (S=0) from any initial condition.

This condition

$$\begin{cases} \lim_{t \to \infty} \dot{S} \mid_{u=0} < 0 \\ \lim_{t \to \infty} \dot{S} \mid_{u=1} > 0 \end{cases}$$

(14)

This condition is satisfied by appropriate selection of the controller coefficients shown in (13) using the existence condition.

**4. 3. Stability Condition** The stability condition ensures that the states errors of the POESLL converter are kept on the origin (S=0). For the constant frequency SMC, this condition is checked by determining the state space equations of the closed loop system and then small signal analysis around their equilibrium points.

**4. 3. 1. State Space Equations of the Closed Loop System** The dynamic equations of the POESLL converter under the constant frequency SMC are obtained by replacing  $u_{eq}$  in (2) with (8) which yields:

$$\begin{cases} L\frac{di_{L}}{dt} = E - \frac{k_{1}E + k_{2}i_{c2} + k_{3} \beta v_{o} - V_{d}}{k_{1} E - v_{o}} E - v_{o} \\ C_{2}\frac{dv_{o}}{dt} = -\frac{k_{1}E + k_{2}i_{c2} + k_{3} \beta v_{o} - V_{d}}{k_{1} E - v_{o}} i_{L} - \frac{v_{o}}{R} \end{cases}$$

(15)

4. 3. 2. Equilibrium Points of the POESLL Converter Suppose that all conditions are satisfied. In origin (S=0), all the state variables of the converter reach the equilibrium points; that is,  $dv_0/dt=di_L/dt=0$ . Then, the equilibrium points of the converter are expressed as:

$$V_{o} = \frac{V_{d}}{\beta}$$

$$I_{L} = \frac{V_{d} - E}{RE}$$

(16)

In (16),  $V_0$ ,  $V_d$  and  $I_L$  are output voltage, voltage reference and inductor current in steady state region, respectively. R and E are output resistance and input voltage.

4. 3. 3. Small Signal Analysis of the Dynamic Equations Equation (15) can be expressed as (17). By using the following static condition  $\beta V_O - V_d = 0$  and the assumption  $V_O >> V_d$ ; then, the linearized equations of the closed loop system can be given as (18).

$$L\frac{d I_{L} + i_{L}}{dt} = E - \frac{a_{1}E + a_{2} \alpha(V_{0} + v_{0} - v_{d})}{a_{1}}$$

$$- \frac{a_{3} \int \alpha V_{0} + v_{0} - v_{d} dt + a_{4}C_{2}d V_{0} + v_{0} / dt}{a_{1}}$$

$$C_{2}\frac{d V_{0} + v_{0}}{dt} = \frac{-a_{1}E - a_{2} \alpha(V_{0} + v_{0} - v_{d})}{a_{1} E - V_{0} - v_{0}}$$

$$- \frac{a_{3} \int \alpha V_{0} + v_{0} - v_{d} dt + a_{4}C_{2}d V_{0} + v_{0} / dt}{a_{1} E - V_{0} - v_{0}} - \frac{V_{0} + v_{0}}{R}$$

(17)

$$\frac{di_{L}}{dt} = b_{11}i_{L} + b_{12}v_{O}$$

$$\frac{dv_{O}}{dt} = b_{21}i_{L} + b_{22}v_{O}$$

(18)

where:

$$b_{11} = \frac{k_2 E}{L \ E - V_d \ \left(k_1 - \frac{k_2 Y_d}{RE}\right)}$$

$$b_{12} = -\frac{k_3 \beta}{L k_1} - \frac{k_2 \ 2V_d - E}{L \ E - V_d \ \left(k_1 - \frac{k_2 Y_d}{RE}\right)R} - \frac{k_3 k_2 \beta V_d}{L k_1 \ k_1 - k_2 Y_d \ / \ RE \ RE}$$

$$b_{21} = -\frac{k_1 E}{C_2 \ E - V_d \ k_1 - k_2 Y_d \ / \ RE}$$

$$b_{22} = \frac{k_1 \ 2V_d - E}{C_2 \ E - V_d \ k_1 - k_2 Y_d \ / \ RE \ R}$$

(19)

205

The characteristics equation of the linearized closed loop system is written as Equation (20).

$$\begin{vmatrix} S - b_{11} & -b_{12} \\ -b_{21} & S - b_{22} \end{vmatrix} = S^2 + d_1 S + d_2 = 0$$

(20)

where:

$$d_1 = -b_{11} - b_{22}, d_2 = b_{11}b_{22} - b_{12}b_{21}$$

(21)

According to Routh criterion, the following conditions must be satisfied to ensure the closed loop stability of the linearized system.

$$d_1 > 0, d_2 > 0 \tag{22}$$

By mathematically solving Equation (19) and replacing into Equation (22), the stability of the closed loop system is determined; then, by using Equation (13) and observing the output voltage response, the proper range of the controller coefficients can be given.

### **5. SIMULATION AND EXPERIMENTAL RESULTS**

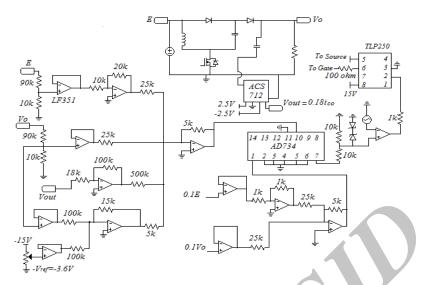

In this section, simulations and experimental results are presented to show the effectiveness of the proposed sliding mode controller for a POESLL converter operated in continuous conduction mode. The coefficients of the proposed controller are selected as:  $k_1=0.015$ ,  $k_2=0.02$ ,  $k_3=0.1$ ,  $\beta=0.1$ . The circuit parameters of the POESLL converter are listed in Table 1. The simulations have been performed in PSIM software. The circuit elements of the converter are listed in Table 2.

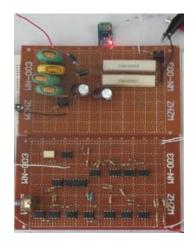

The laboratory model of the POESLL converter under the proposed controller is shown in Figure 3. The proposed system has been implemented in analogue platform. From Figure 3, it can be seen that the equivalent control law is implemented using Op- Amps; then, it is compared with a saw tooth waveform to generate the switching signal. The obtained signal is given to the switch (MOSFET) using an optocoupler (TLP250).

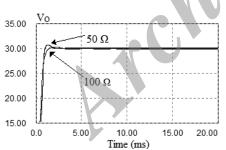

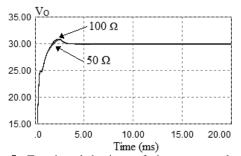

**5. 1. Simulations Results** Figure 4 shows the transient behaviour of the output voltage of the POESLL converter for E=9V and R=50, 100  $\Omega$ . Figure 5 shows the transient behaviour of the output voltage of the POESLL converter for E=12V and R=50, 100  $\Omega$ . From Figures 4 and 5, it can be seen that the voltage of the converter under the proposed controller has a quick settling time and small overshoot.

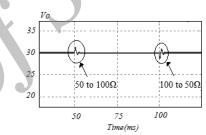

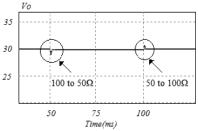

Figure 6 depicts the behavior of the output voltage of the POESLL converter for E=9 V and load change between 50 and 100  $\Omega$ . It is clear that the voltage of the POESLL converter under the proposed controller has a

small overshoot and quick settling time. Figure 7 shows the response of the output voltage of the POESLL converter for E=12 V and load change between 100  $\Omega$ and 50  $\Omega$ . It can be seen that the output voltage of the POESLL converter under the proposed controller has a small overshoot and quick settling time.

**TABLE 1.** Parameters of the converter

| Name                                    | Symbol                          | Value                     |

|-----------------------------------------|---------------------------------|---------------------------|

| Output voltage                          | Vo                              | 30V                       |

| Reference voltage                       | $\mathbf{V}_{\mathrm{d}}$       | 3V                        |

| Input voltage                           | Е                               | 9, 12V                    |

| Inductor                                | L                               | 0.0004H                   |

| Capacitor                               | C <sub>1</sub> , C <sub>2</sub> | 0.0001F                   |

| Output resistance                       | R                               | $50\Omega$ to $100\Omega$ |

| Frequency switching                     | F                               | 20kHz                     |

| Equivalent series resistor of inductor  | ESRL                            | 0.35Ω                     |

| Equivalent series resistor of capacitor | ESRC                            | .02Ω                      |

| <b>TABLE 2.</b> Elements of the converter |                            |  |

|-------------------------------------------|----------------------------|--|

| Name                                      | Туре                       |  |

| Switch                                    | IRFZ470                    |  |

| Diode                                     | 1N555                      |  |

| Capacitor                                 | 0.0001F/100V(electrolytic) |  |

| Inductor                                  | 4×0.0001H/5A               |  |

| Op Amp                                    | LF351                      |  |

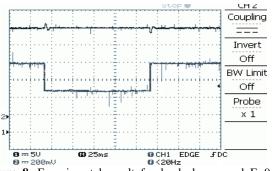

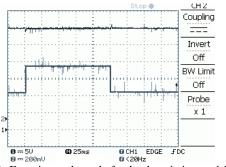

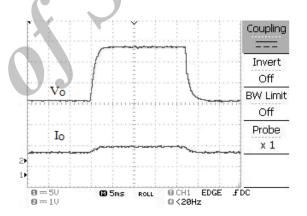

**5.2. Experimental Results** Figure 8 shows the experimental response of the voltage for E=9 V and load change between 50  $\Omega$  and 100  $\Omega$ . Figure 9 shows the experimental behaviour of the voltage for E=12 V and load change between 50  $\Omega$  and 100  $\Omega$ . It is clear that the closed loop system is stable in different operating conditions.

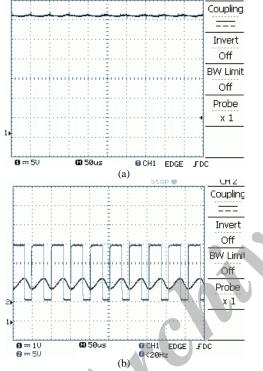

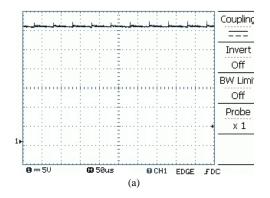

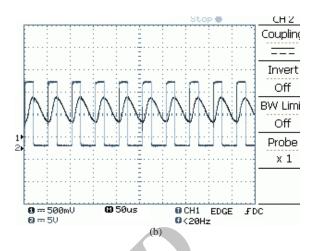

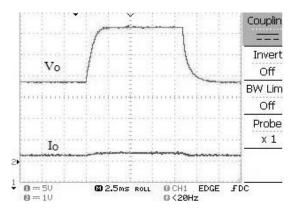

Figures 8 and 9 demonstrate the effectiveness of the POESLL converter under the proposed controller. Figures 10.a and b show the output voltage, switching signal and inductor current of the POESLL converter in steady state region for E=9V and R=50 $\Omega$  and V<sub>0</sub>=30 V. Figures 11.a and b show the output voltage and switching signal and inductor current of the POESLL converter in steady state region for E=12V and R=100 $\Omega$  and V<sub>0</sub>=30 V.

Figure 12 depicts the response of the voltage of the POESLL converter for E=9 V and R=50  $\Omega$  and voltage change between 18 and 30 V.

Figure 3. Laboratory model of the POESLL converter under the constant frequency SMC

Figure 13 depicts the response of the voltage of the POESLL converter for E=12 V and R=100  $\Omega$  and voltage change between 30 V and 42 V.

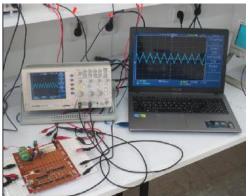

Figure 14 shows the laboratory model of the proposed system in analogue platform.

In summary, from Figures 10 and 11, it is found that the switching frequency is 20 kHz and the POESLL works in continuous conduction mode. Moreover, the simulation results of the POESLL converter under the proposed controller match the experimental results with a maximum tolerance of 1%.

Figure 4. Transient behaviour of the output voltage for E=9 V

Figure 5. Transient behaviour of the output voltage for E=12V

Figure 6. Output voltage of the POESLL converter for E=9 V and load variations between 50 and 100  $\Omega$

Figure 7. Output voltage of the POESLL converter for E=12 V and load variations between 100 and 50  $\Omega$

**Figure 8.** Experimental result for load change and E=9 V [Ch1:5V/Div-output voltage, Ch2:200mV/Div-load]

Figure 9. Experimental result for load variation and E=12V [Ch1:5V/Div-output voltage, Ch2:200mV/Div-load]

**Figure 10.** Experimental response of the output voltage of the POESLL converter for E=9 V and  $R=50 \Omega$  in steady state region; (a) Response of the output voltage [Ch1:5 V/Divoutput voltage] (b) Response of the switching signal and inductor current [Ch1:1 V/Div-inductor current and Ch2:5 V/Div-switching signal]

**Figure 11.** Experimental response of the output voltage of the POESLL converter for E=12V and  $R=100 \Omega$  in steady state region (a) Response of the output voltage [Ch1:5 V/Divoutput voltage] (b) Response of the switching signal and inductor current [Ch1:1 V/Div-inductor current and Ch2:5 V/Div-switching signal]

Figure 12. Experimental result for E=9 V and R=50  $\Omega$  and output voltage change between 30 V and 42 V[Ch1:5V/Div-output voltage and Ch2:1V/Div-load]

Figure 13. Experimental result for E=12 V and R=100  $\Omega$  and output voltage change between 30 and 42 V [Ch1:5V/Divoutput voltage and Ch2:1V/Div-load] output voltage and Ch2:1V/Div-load]

Figure 14. Laboratory model of a POESLL converter using a constant frequency SMC

### **6. CONCLUSIONS**

In this paper, the design of a constant frequency SMC for output voltage regulation of the POESLL has been successfully presented. The constant frequency sliding mode control scheme has been implemented. The proposed controller ensures robustness and stability against load and input voltage variations compared with linear controllers. Simulation and experimental results are presented to show the performance of the proposed controller. The proposed controller is suitable for most commercial applications. The advantages of the proposed controller implemented in this paper are: constant frequency, simple implementation, robustness performance against load and voltage variations and less number of sensors.

### **7. REFERENCES**

Hegazy, O., Van Mierlo, J. and Lataire, P., "Analysis, modeling, and implementation of a multidevice interleaved dc/dc converter for fuel cell hybrid electric vehicles", *Power Electronics, IEEE Transactions on*, Vol. 27, No. 11, (2012), 4445-4458.

- Silva-Ortigoza, R., Hernández-Guzmán, V.M., Antonio-Cruz, M. and Munoz-Carrillo, D., "Dc/dc buck power converter as a smooth starter for a dc motor based on a hierarchical control", *Power Electronics, IEEE Transactions on*, Vol. 30, No. 2, (2015), 1076-1084.

- Luo, F.L. and Ye, H., "Positive output super-lift converters", *Power Electronics, IEEE Transactions on*, Vol. 18, No. 1, (2003), 105-113.

- Biolkova, V., Kolka, Z. and Biolek, D., "State-space averaging (ssa) revisited: On the accuracy of ssa-based line-to-output frequency responses of switched dc-dc converters", WSEAS Transactions Circuits System Vol. 2, (2010), 81-90.

- Merdassi, A., Gerbaud, L. and Bacha, S., "Automatic generation of average models for power electronics systems in vhdl-ams and modelica modelling languages", *Journal of Modelling and Simulation of Systems*, Vol. 1, No. 3, (2010), 176-186.

- Mattavelli, P., Rossetto, L. and Spiazzi, G., "Small-signal analysis of dc-dc converters with sliding mode control", *Power Electronics, IEEE Transactions on*, Vol. 12, No. 1, (1997), 96-102.

- ME, R.S.R.B., ME, S.D. and ME, S.J., "A closed loop control of quadratic boost converter using pid controller", *International Journal of Engineering-Transactions B: Applications*, Vol. 27, No. 11, (2014), 1653-1662.

- Rad, M.J. and Taheri, A., "Digital controller designbased on time domain for dc-dc buck converter", *International Journal* of Engineering-Transactions B: Applications, Vol. 28, No. 5, (2015), 693-700.

- Maksimovic, D. and Zane, R., "Small-signal discrete-time modeling of digitally controlled pwm converters", *Power Electronics, IEEE Transactions on*, Vol. 22, No. 6, (2007), 2552-2556.

- Sarvi, M., Derakhshan, M. and Sedighizadeh, M., "A new intelligent controller for parallel dc/dc converters", *International Journal of Engineering-Transactions A: Basics*, Vol. 27, No. 1, (2013), 131-142.

- Alfi, A., Hajizadeh, A. and Gholizade, N.H., "Optimal state feedback control design and stability analysis of boost dc-dc converters in fuel cell power systems using pso", *International Journal of Engineering-Transactions A: Basics*, Vol. 27, No. 1, (2013): 131-141

- Salimi, M., Soltani, J., Markadeh, G.A. and Abjadi, N.R., "Indirect output voltage regulation of dc-dc buck/boost converter operating in continuous and discontinuous conduction modes using adaptive backstepping approach", *Power Electronics, IET*, Vol. 6, No. 4, (2013), 732-741.

- 13. Utkin, V., Guldner, J. and Shi, J., "Sliding mode control in electro-mechanical systems, CRC press, Vol. 34, (2009).

- Umamaheswari, M.G., Uma, G. and Vijayalakshmi, K., "Design and implementation of reduced-order sliding mode controller for higher-order power factor correction converters", *Power Electronics, IET*, Vol. 4, No. 9, (2011), 984-992.

- Kumar, K.R. and Jeevananthan, S., "Design and implementation of reduced-order sliding mode controller plus proportional double integral controller for negative output elementary superlift luo-converter", *Power Electronics, IET*, Vol. 6, No. 5, (2013), 974-989.

- Chen, Z., Hu, J. and Gao, W., "Closed-loop analysis and control of a non-inverting buck-boost converter", *International Journal of Control*, Vol. 83, No. 11, (2010), 2294-2307.

- Chen, Z., Gao, W., Hu, J. and Ye, X., "Closed-loop analysis and cascade control of a nonminimum phase boost converter", *Power Electronics, IEEE Transactions on*, Vol. 26, No. 4, (2011), 1237-1252.

- Chen, Z., "Pi and sliding mode control of a cuk converter", *Power Electronics, IEEE Transactions on*, Vol. 27, No. 8, (2012), 3695-3703.

- Kumar, K.R. and Jeevananthan, S., "Hysteresis modulation based sliding mode control for positive output elementary super lift luo converter", *International Journal of Electrical and Electronics Engineering*, Vol. 2, No. 3, (2009), 131-138.

- Kumar, K.R. and Jeevananthan, S., "Sliding mode control for current distribution control in paralleled positive output elementary super lift luo converters", *Journal of Power Electronics*, Vol. 11, No. 5, (2011), 639-654.

- Fateh, M.M., Alfi, A., Moradi, M. and Modarres, H., "Sliding mode control of lorenz chaotic system on a moving fuzzy surface", in EUROCON'09. IEEE, (2009), 964-970.

- 22. Tan, S.-C., Lai, Y.-M., Tse, C.K., Martínez-Salamero, L. and Wu, C.-K., "A fast-response sliding-mode controller for boost-

type converters with a wide range of operating conditions", *Industrial Electronics, IEEE Transactions on*, Vol. 54, No. 6, (2007), 3276-3286.

- Tan, S.-C., Lai, Y.-M. and Tse, C.K., "General design issues of sliding-mode controllers in dc–dc converters", *Industrial Electronics, IEEE Transactions on*, Vol. 55, No. 3, (2008), 1160-1174.

- He, Y., Xu, W. and Cheng, Y., "A novel scheme for slidingmode control of dc-dc converters with a constant frequency based on the averaging model", *Journal of Power Electronics*, Vol. 10, No. 1, (2010), 1-8.

- Dupont, F.H., Rech, C., Gules, R. and Pinheiro, J.R., "Reducedorder model and control approach for the boost converter with a voltage multiplier cell", *Power Electronics, IEEE Transactions* on, Vol. 28, No. 7, (2013), 3395-3404.

# c SI

# Design and Implementation of a Constant Frequency Sliding Mode Controller for a Luo Converter

### A. Goudarzian, H. Nasiri, N. Abjadi

Faculty of Engineering, Shahrekord Univercity, Shahrekord, Iran

### PAPER INFO

Paper history: Received 19 May 2015 Received in revised form 08 September 2015 Accepted 26 January 2016

Keywords: POESLL Converter Constant Frequency Sliding Mode Controller Laboratory Prototype در این مقاله، یک کنترلکننده مقاوم برای تنظیم ولتاژ مبدل POESLL در حالت هدایت پیوسته معرفی شده است. مبدل POESLL یک مبدل DC/DC با بهرهی انتقال ولتاژ بالاست. از این مبدل میتوان در منابع توان ثابت، سیستمهای مخابراتی و کاربردهای صنعتی استفاده کرد. به خاطر عملکرد کلیدزنی، ساختار مبدل DESLL غیرخطی است. علاوه بر این، به خاطر نوسانات بار و ولتاژ ورودی، ساختار این مبدل متغیر با زمان است. به منظور بهبود عملکرد و تنظیم ولتاژ خروجی، مبدل نیاز به یک کنترلکنندهی مقاوم دارد. کنترلکنندهی پیشنهادشده در این مقاله بر اساس روش کنترل مد لغزشی فرکانس ثابت طراحی میشود. کنترلکنندههای مد لغزشی متناسب با ساختار غیرخطی و متغیر با زمان مبدلهای DC/DC هستند. عملکرد کنترلکننده ییشنهادشده در این مقاله بر اساس روش کنترل مد یک نمونه از آن ساخته شده است. در این مقاله، طراحی، شبیهسازی و نتایج عملی ارائه میشوند تا عملکرد مؤثر کنترلکننده پیشنهادی برای تنظیم ولتاژ خروجی مبدل DOSLL را نشان دهند.

doi: 10.5829/idosi.ije.2016.29.02b.09

*چکید*ه