ENTERNATIONAL CONFERENCE ON

:Id

Istanbul-Turkey

ND TECHNOL

14 March 2016

C

IN SCIENCE

ركيه - استانبول ۲۴ اسفند ١٣٩.٢

### Comparative Study of Trigate SOI FinFET and Trigate JL SOI FinFET Structures

**B.Fakhr**

Department of Electrical Engineering, Neyshabur Branch, Islamic Azad University, Neyshabur, Iran mkh23424@yahoo.com

\*S.E.Hosseini

Department of Electrical Engineering, Mashhad Branch, Ferdowsi University, Mashhad, Iran e\_hosseini\_98@yahoo.com

### Abstract

This paper investigates the effect of channel length variations on transistor perfomane for the Trigate SOI FinFET and Trigate Junctionless SOI FinFET. compaires the variations in threshold voltage, transeconductance, subthreshold swing,  $I_{ON}/I_{OFF}$  ratio and  $r_o$ .

Keywords: FinFET, Junctionless, SOI, SCEs,  $V_{th}$  , subthreashold slop,  $I_{\text{ON}}/I_{\text{OFF}}\textbf{.}$

### RESEARCH IN SCIENCE AND TECHNOLOGY

Istanbul-Turkey 1

14 March 2016

### Introduction

As the gate length decreases the gate control over the channel also decrease due to the proximity of source and drain. The gate can be placed close to the channel by taking ultra thin body known as fin type structure and tighter gate coupling can be achieved by increasing the number of gates from single gate to multi gates. The multi gate FinFET transistors are very promising alternatives to planar devices in sub 50nm gate length regime. The tri gate FinFET [1] is one of the promising structures in nano scale regime. The tri gate FinFET provides a symmetric device architecture where the channel is controlled by gate from three sides of the Si film. The FinFET can be fabricated on either bulk silicon (bulk-Si) or silicon-on-insulator wafer substrates [2],[3]. FinFETs have advantages like a higher I<sub>ON</sub>/I<sub>OFF</sub> ratio (very important for digital circuits) and smaller intrinsic gate capacitances and design flexibility at with multiple gates [4]. The junctionless transistor is considered as one of the most promising candidates for nanometer scale CMOS integrated circuits [5]. The concept of the junctionless(JL) nanowire transistor(JNT), which contains a single-doping species at the same level in its source, drain, and channel, has been investigated [6-13]. The advantages of JL devices include: 1) avoidance of the use of an ultra shallow source/drain junction, which greatly simplifies the process flow; 2) low thermal budgets owing to implant activation anneal after gate stack formation is eliminated; and 3) the current transport being in the bulk of the semiconductor, which reduces the impact of imperfect semiconductor/insulator interfaces. However, the JNT devices require a silicon-on insulator (SOI) wafer and a uniform ultra thin channel to turn the device off, making them technologically difficult and expensive to produce. In this paper Trigate SOI FinFET and Trigate Junctionless SOI FinFET have been compared using extensive device simulations and investigated in the sence of electrical characteristics.

### DEVICE STRUCTRURE AND SPECIFICATION

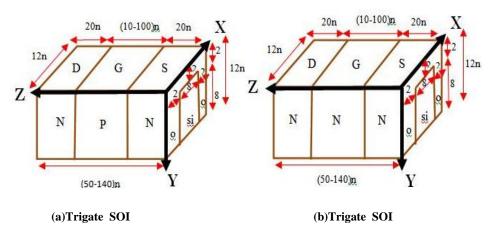

The transistor structures are illustrated in Fig. 1.

Fig.1. Three dimensional view of FinFET's

The transistors under investigate have following specifications: physical models are performed for the following n-channel FinFET designs: physical gate length  $L_G=(10-100)$ nm, gate oxide thickness  $t_{OX}=2$ nm and supply voltage VDD=1V, channel doping N-type=1e19 and P-type=1e17. n-channel Junctionless FinFET has physical gate length  $L_G=(10-100)$ nm, gate oxide thickness  $t_{OX}=2$ nm and

supply voltage VDD=1V. channel doping N-type=1e19. The device parameters for Trigate SOI FinFET and Trigate Junctionless SOI FinFET have been sumerized in Table1.

| Device<br>parameter       | <b>Tableate De</b><br>SOI FinFET | Tri-gate<br>v <b>ice</b><br>Junctionless SOI<br>FinFET |

|---------------------------|----------------------------------|--------------------------------------------------------|

| Channel<br>Length (nm)    | 10-100                           | 10-100                                                 |

| t <sub>ox</sub> (nm)      | 2                                | 2                                                      |

| Gate work<br>function(eV) | 4.30                             | 4.30                                                   |

| Channel<br>Doping         | N=1e19<br>P=1e1 <sup>v</sup>     | 1e19 (n-type)                                          |

Electrical characteristics for the devices are simulated using 3D device simulator ATLAS Version 3.20.2.R[14]. The gate and the drain voltages are swept from -1 to +1 V and 0 to 1V respectively. The physical gate length is changed between 10 to 100 nm. The transfer and the output characteristics, threshold voltage, subthreshold slope and drain induced barrier lowering (DIBL),  $g_m$ ,  $I_{on}/I_{off}$  ratio,  $r_o$  are studied.

#### **RESULTS AND DISCUSSION**

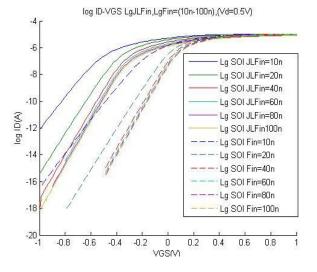

The  $I_D$ -V<sub>G</sub> characteristics of transistors are shown in Fig.2.

Fig 2. Simulated Trigate SOI FinFET and Trigate Junctionless SOI FinFET transfer characteristic (I<sub>D</sub>-V<sub>G</sub>)

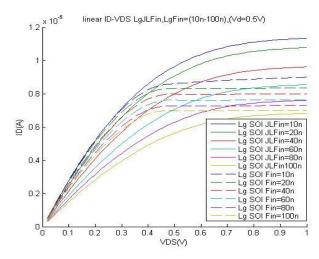

Simulation results show that both Trigate SOI FinFET and Trigate Junctionless SOI FinFET have low leakage current. The  $I_D$ - $V_D$  characteristics of the transistors are shown in Fig.3. Simulation results show that Trigate SOI FinFET has better output characteristic and higher ON currents when the channel length gets smaller.

# RESEARCH IN SCIENCE AND TECHNOLOGY

14 March 2016

Istanbul-Turkey

Fig.3. Simulated Trigate SOI FinFET and Trigate Junctionless SOI FinFET output characteristic (I<sub>D</sub>-V<sub>D</sub>)

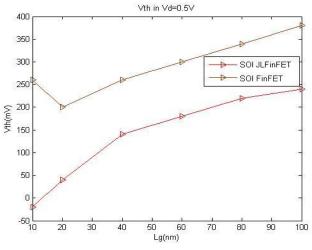

### A.Variation in Threshold Voltage (V<sub>th</sub>)

The change in threshold voltage with the channel length is shown in Fig.4. Although the threshold voltage of a MOSFET is not a figure of merit for device/circuit performance, it is the most important parameter for MOS device modelling and circuit design [15-17]. The result shows that threshold voltage is lower when channel length is scaled down therefore making it a good choice at smaller channel lengths.

Fig.4. Vth versus to Lg variation

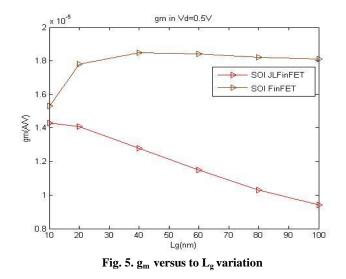

B. g<sub>m</sub>

Fig. 5. shows  $g_m$  characteristics verses different channel lengths.  $G_m$  of the Trigate SOI FinFET is higher than that of the Trigate Junctionless SOI FinFET. This shows that FinFET exhibits higher voltage gain in analoge applications.

### RESEARCH IN SCIENCE AND TECHNOLOGY

دومین کنفرانی بین المللے یزوهنتر درعلوم وتکنولوز ، سے

Istanbul-Turkey

14 March 2016

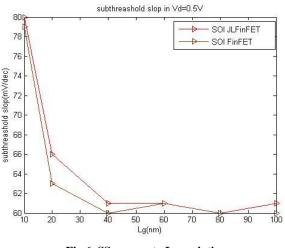

#### C. Variation in subthreshold swing (SS)

Subthreshold swing is defined as the voltage change required to increase the drain current one order of magnitude[18]. Sub-threshold swing is a very critical parameter for a transistor[19]. Theoretical limit of sub-threshold swing of a MOSFET is 60 mV/decade[20]. Fig.6. shows the change in subthreshold swing with respect to channel length. Trigate SOI FinFET shows better subthreshold swing compared to Trigate Junctionless SOI FinFET at gate lengths below 60nm.

Fig.6. SS versus to  $L_g$  variation

#### D. $I_{on}/I_{off}$ ratio

$I_{on}/I_{off}$  ratios are critically affected when channel length comes down to the scale of 20 nm[20]. Fig.7. shows  $I_{on}/I_{off}$  ratio verses channel length. There is no much difference  $I_{on}/I_{off}$  ratio between Trigate SOI FinFET and Trigate Junctionless SOI FinFET.  $I_{on}/I_{off}$  ratio is better in some channel lengths for Trigate SOI FinFET and in other channel lengths for Trigate Junctionless SOI FinFET.

## RESEARCH IN SCIENCE AND TECHNOL GY

14 March 2016

Istanbul-Turkey

دومین کنفرانی بین المللے یزوهنتر درعلوم و تکنولوز ، ا ترکیه - استانبول ۲۴ اسفند ۱۳۹۴

log(lon/loff) in ∨d=0.5∨ 14 SOI JLFinFET SOI FinFET 13 12 (fton/loff) 11 10 9 8 712 90 20 30 40 60 70 100 Lg(nm)

Fig.7.  $I_{on}/I_{off}$  ratio versus to  $L_g$  variation

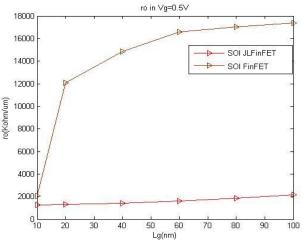

#### E.r<sub>o</sub>

Fig.8. shows the output resistance characteristics verses different channel length. The  $r_0$  of the Trigate SOI FinFET is higher than that of the Trigate Junctionless SOI FinFET. Higher output resistance along with high trancecondctance reveals that FinFET has higher gain which is very important in analoge and digital applications.

Fig.8.  $r_o$  versus to  $L_g$  variation

### CONCLUSIONS

In this work, the short channel effects of Trigate SOI FinFET and Trigate Junctionless SOI FinFET for different channel lengths has been analyzed through device simulations. Results show that Trigate SOI FinFET have higher  $V_{th}$ ,  $g_m$ ,  $r_o$  and lower subthreshold slop in the scaled channel lengths. This means that FinFET with source and drain junctions to channel has better performance compaired to junctionless counterpart.

### Arghingerfational conference on RESEARCH IN SCIENCE AND TECHNOLOGY

Istanbul-Turkey 14 March 2016

### References

- [1]. Fossum, J.W.Y.a.J.G., , "On the feasibility of nano-scale triple

- gate transistors," IEEE Trans. Electron Device Letters, vol. 52, no. 6, pp. 1159-1164, Jun 2005.

- [2]. C.-H. Lin, R.K., R. J. Miller, T. B. Hook, A. Bryant, P.O. W. Haensch, I. Lauer, T. Yamashita, V. Basker, T. Standaert, and E.L. K. Rim, H. Bu, and M. Khare, "Channel doping impact on FinFETs for 22 nm and beyond," in Proc. Symp. VLSI Tech. Dig., Jun. 2012, pp. 15–16.

- [3]. C.-Y. Chang, T.-L.L., C. Wann, L.-S. Lai, H.-M. Chen, C.-C. Yeh, et al., "A 25-nm gate-length FinEET transistor module for 32 nm node," in IEDM Tech. Dig. Dec. 2009, pp. 1-4.

- FinFET transistor module for 32 nm node," in IEDM Tech. Dig., Dec. 2009, pp. 1–4.

[4]. Ghai, D., S.P. Mohanty, and G. Thakral. "Comparative analysis of double gate FinFET configurations for analog circuit design". in Circuits and Systems (MWSCAS), 2013 IEEE 56th International Midwest Symposium on. 2013.

- [5]. J. P. Colinge, C.W.L., A. Afzalian, N. D. Akhavan, R. Yan, P.R. I. Ferain, B. O'Neill, A. Blake, M. White, A. M. Kelleher, and a.R.M. B. McCarthy, "Nanowire transistor without junctions," Nature Nanotechnol., vol. 5, no. 3, pp. 225–229, 2010.

- [6]. C.-W. Lee, A.A., N. D. Akhavan, R. Yan, I. Ferain, and J. P. and Colinge, "Junctionless multigate fieldeffect transistor," Appl. Phys. Lett.

- [7]. J.-P. Colinge, C.-W.L., A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, B.O.N. P. Razavi, A. Blake, M. White, A.-M. Kelleher, B. McCarthy, and and R.Murphy, "Nanowire transistors without Junctions," Nat. Nanotechnol.,vol. 5, no. 3, pp. 225–229, Mar. 2010.

- [8]. J. P. Colinge, C.-W.L., I. Ferain, N. D. Akhavan, R. Yan, R. Razavi, A.N.N. R. Yu, and R. T. Doria, "Reduced electric field in junctionless, and transistors, ," Appl. Phys. Lett., vol. 96, no. 7, pp. 073510-1–073510-3, Feb. 2010.

- [9]. A. Kranti, R.Y., C.-W. Lee, I. Ferain, R. Yu, N. D. Akhavan, and a.J.P.C. P. Razavi, "Junctionless nanowire transistor (JNT): Properties and design guidelines," Solid State Electron., vol. 65/66,pp. 33– 37, Nov./Dec. 2011.

- [10]. R. Yu, S.D., I. Ferain, P. Razavi, M. Shayesteh, A. Kranti, R. Duffy, and and C.W.L. J. P. Colinge, A. Afzalian, N. D. Akhavan, R. Yan,, "Device design and estimated performance for p-type junctionless transistors on bulk germanium substrates," IEEE Trans. Electron Devices, vol. 59, no. 9, pp. 2308–2313, Sep. 2012.

- [11]. H.-C. Lin, C.-I.L., and T.-Y. Huang, , "Characteristics of n-type junctionless poly-si thin-film transistors with an ultrathin channel," IEEE Electron Device Lett., vol. 33, no. 1, pp. 53–55, Jan. 2012.

- [12]. C.-J. Su, T.-I.T., Y.-L. Liou, Z.-M. Lin, H.-C. Lin, and T.-S. Chao,, "Gate-all-around junctionless transistors with heavily doped polysilicon nanowire channels," IEEE Electron Device Lett., vol. 32, no. 4, pp. 521–523, Apr. 2011.

- [13]. R. Rios, A.C., M. Armstrong, A. Budrevich, H. Gomez, and N.R.-O. R. Pai, and K. Kuhn,, "Comparison of junctionless and conventional trigate transistors with Lg down to 26 nm,"IEEE Electron Device Lett., vol. 32, no. 9, pp. 1170–1172, Sep. 2011.

- [14]. Atlas User's Manual: Device Simulation Software, 2010.

- [15]. Ortiz-Conde A, R.J., Garcia Sanchez FJ, Liou JJ, "An improved definition for modeling the threshold voltage of MOSFETS". Solid-State Electron 1998; 42: 1743-6.

- [16]. Salcedo JA, O.-C.A., Garcia Sanchez FJ,Muci J, Liou JJ, Yue Y, "New approach for defining the threshold voltage of MOSFETs". IEEE Trans Electron Devices 2001; 48:809-13.

- [17]. Benson J, D.H.N., Redman-White W, Easson CA, Uren MJ,Faynot O, Pelloie JL, "A physically based relation between extracted threshold voltage and surface potential flat band voltage for MOSFET compact modeling". IEEE Trans Electron Devices 2001; 48: 1019-21.

- [18]. Singhal, S., et al. "Comparative study of Double Gate SOI FinFET and trigate Bulk MOSFET structures". in Engineering and Systems (SCES), 2013 Students Conference on. 2013.

- [19]. Doyoung Jang, J.W.L., Chi-Woo Lee, Jean-Pierre, L.M. Colinge, Jung II Lee, Gyu Tae Kim and Gérard, and Ghibaudo, "Low-frequency noise in Junction-less multigate transistors". Applied Physics Letters 98, 133502 (2011).

- [20]. Al Sayem, A., Y. Arafat, and M. Rahman. "Effect of high k-dielectric as gate oxide on short channel effects of junction-less transistor". in Advances in Electrical Engineering (ICAEE), 2013 International Conference on. 2013.