Istanbul-Turkey 14 March 2016

وهنتردرعلوم وتكنولوزاك

### Output Impedance Improvement of A Low Voltage Low Power Current Mirror Based on Bulk Driven Technique

### Yasin Bastan

Ph. D. student Faculty of Electrical Engineering, Electronics Department, Shahid Rajaee Teacher Training University Tehran, Iran Ybastan.ee@gmail.com

#### **Elahe Hamzehil**

M.Sc. student Faculty of Electrical Engineering, Electronics Department, Shahid Rajaee Teacher Training University Tehran, Iran Elahe\_hamzehil@yahoo.com

#### **Parviz Amiri**

Assistant Professor Faculty of Electrical Engineering, Electronics Department, Shahid Rajaee Teacher Training University Tehran, Iran PAmiri@srttu.edu

#### **Masoume Haeri**

M.Sc. student, Faculty of Electrical Engineering, Electronics Department, Hadaf Institute of Higher Education, sari, Iran Masoume.haeri@yahoo.com

#### Abstract

This paper improved the output impedance of an LVLP current mirror by using bulk driven technique and transconductance enhancement. The applied technique increases the output impedance of current mirror significantly compared with the primary circuit. Also, it provide little improvement in input resistance and bandwidth. Operation principle of current mirror circuit with proposed improvement is discussed, the most important formulas are derived and compared with the primary circuit and its performance is verified by simulation in 0.18um technology. An output resistance of 39.5 G $\Omega$  is achieved for the improved circuit that shows 5G $\Omega$  increment in comparison with primary circuit. Besides, simulation results show an input resistance of 12.8  $\Omega$  and -3dB cut-off frequency of 216 MHz for the improved current mirror circuit while it consumes only 42.5  $\mu$ W still and other specifications are still remain unchanged. Simulation is done by 1V power supply and 15 $\mu$ A input current.

**Keywords:** Low Power Current Mirror; Bulk Driven technique; High output Impedance; CMOS

Istanbul-Turkey 14 March 2016

1791 Julian

#### Introduction

Current mirrors are one of the most important and efficient block of each analogue integrated circuit due to providing bias conditions and active loading role, thus optimum design has significant influence on circuit performances enhancement. Accuracy, linearity, output and input impedance, bandwidth and noise are the factors of the current mirrors which should be considered for optimum design (Azhari et al, 2011). On the other hand, in recent years low voltage and low power circuit designs are a substantial point according to frontier of knowledge in integrated circuit designs (Yani et al, 2010).

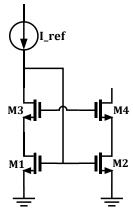

High output impedance is one of the most important factor of each current mirror that many methods are proposed to achieve it. Cascode structure is a traditional method that supports this idea (Gabbouj et al, 2008), (Zhu et al, 2008). In some cases, QFGMOS transistors are used to increase output impedance (Raj et al, 2014). In some papers, presented a feedback gain stage to enhance this factor (Hsing et al, 2001). Also, in some cases, the features of the feedback structures such as shunt type is used to increase the output impedance (Sharma et al, 2006). Figure 1 shows another structure that not only does it increases output impedance but also enhance accuracy by equalization of drain-source voltage and decreasing channel length modulation. However, Conventional cascode current mirrors need more power supply. Thus due to importance of low voltage low power technology, some methods are considered to minimize voltage and power. For instance, using FGMOS transistors (Sharma et al, 2006) or bulk driven technique are suggested (Murphy et al, 2005).

Besides all benefits, some drawbacks are reported for these methods. For example, current offset problem and low bandwidth are reported as a consequence of using bulk driven technique (Azhari et al, 2011). So, achieving advantages of this idea needs wise and accurate circuit design to have an LVLP current mirror with bulk driven structure. Also, minimizing transistors width and length is another way to decrease power supply but nowadays, it has been limited by technology (Yani et al, 2010).

This paper improve the performance and the output impedance of an LVLP current mirror by using bulk driven technique. In section 2 and 3 the main concepts of idea are described and circuit analysis of current mirror is presented in section 4. Simulation results are presented in Section 5. Finally, the paper is concluded in Section 6.

Fig 1. Cascode current mirror with high output impedance

#### Bulk driven and gm boosting

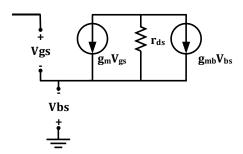

Almost, depending on the applied technology the bulk of MOSFET transistor is connected to source terminal or power supply,  $V_{dd}$  (or  $V_{ss}$ ) (Haga et al, 2005), in integrated circuit designs. But in some applications, this terminal can be used in another ways. Sometimes the bulk terminal connects to a dc bias voltage and will effect on bias conditions, which is known as body bias technique (Volta, 1832). Body driven technique modifies the effective  $g_m$  of MOSFET that it can change the circuit parameters. Fig. 2 illustrates the small signal model of a MOSFET with body effect.

According to nature rules of each transistor, following equations show g<sub>mb</sub> calculation (Razavi, 2007):

تركيه - استانبول ٢٢ اسفند ١٣٩٤

Istanbul-Turkey 14 March 2016

$$g_{mb} = \frac{\partial I_D}{\partial V_{BS}} = \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH}) \left( -\frac{\partial V_{TH}}{\partial V_{BS}} \right)$$

(1)

$$\frac{\partial V_{TH}}{\partial V} = -\frac{\partial V_{TH}}{\partial V} = -\frac{\gamma}{2} \left( 2\varphi_F + V_{SB} \right)^{-\frac{1}{2}}$$

(2)

$$\frac{\partial V_{BS}}{\partial m_b} = g_m \frac{\partial V_{SB}}{2\sqrt{2\varphi_F + V_{SB}}} = \eta g_m$$

(3)

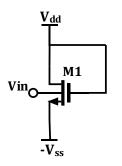

The first time, Balock et al. used bulk driven method for MOSFET analogue circuit design (Rajput and Jamuar, 2002). The aim of this work (Rajput and Jamuar, 2002) was any signal processing it is required some drain bias current to do. Gate driven circuits prepare this current when the gate voltage exceeds MOS threshold voltage, but in bulk driven circuits that is shown in Fig. 3, input signal is applied to bulk terminal and transistor is set in saturation region to make constant drain current.

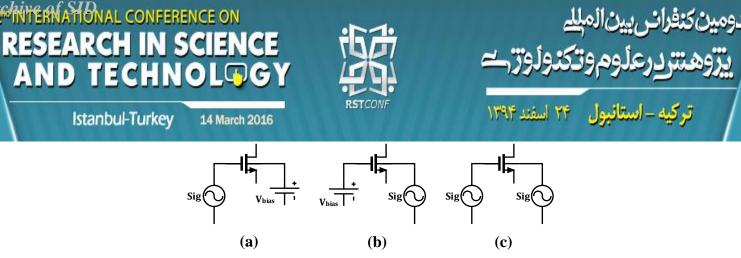

This technique is useful in low voltage application. In the general case, bulk terminal is used in one of the three forms as follow. In first form that is shown in Fig. 4 (a), input signal is applied to gate terminal while bulk terminal effects on bias point through  $V_{\text{bias}}$  (Haga et al, 2005). Next form situation is vice versa, input signal is applied to bulk and bias voltage is connected to gate (Fig. 4 (b)) (Sharma et al, 2006). The final form which is the base of this paper idea, two input signals are applied, one of them is applied to gate and another one is applied to bulk terminal. Fig. 4 (c) shows this form clearly (Ebrahimi et al, 2015).

Fig 2. Small signal model of MOSFET with bulk terminal.

Fig 3. Bulk driven technique

Fig 4. Body and gate derive techniques.

This technique also is used in differential pairs for some important applications (Rajput and Jamuar, 2002). One of the disadvantage of this idea is linearity problem in current mirror circuits, because the last transistor sets in saturation region thus input and output current do not have linearity, unlike in the gate driven current mirror. There are some suggestions to solve this problem according to applications (Yani et al, 2010).

#### Styling Current mirror performance enhancement by body driven technique

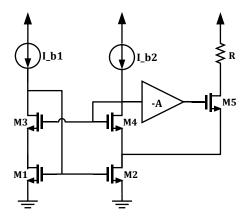

This paper presents an LVLP current mirror with high output impedance by applying the body driven technique to the current mirror circuit is proposed in (Azhari et al, 2011) that Fig. 5 shows the circuit diagram. Negative and positive feedbacks, the basic concept of the circuit, result in parameters improvement, such as high output impedance, low input impedance, desired BW, accuracy and low current transfer error.

The proposed idea is applying an extra signal to bulk terminal of M5 which is shown in Fig. 5. This new signal path that is shown with dash-line in Fig. 6, enhances the output impedance and improves the current transfer error of LVLP current mirror through effective gm boosting. It is worth mentioning that not only does the proposed idea have no bad effect on the other parameters, but also it improves them slightly.

Fig 5. Current mirror circuit proposed in [1]

تركيه – استانبول

۲۴ اسفند ۱۳۹۴

Istanbul-Turkey

14 March 2016

Fig 6. Schematic of current mirror with proposed idea.

#### PROPOSED CIRCUIT ANALYSIS

#### A. Principle of operation

The proposed circuit of this paper is based on circuit is shown in Fig. 5 which includes cascode current mirror comprised of four transistors M1-M4 that M4 is diode connected to have high output swing (Azhari et al, 2011). The output signal from drain of M4 transferred to M5 through gain boosting part (MA and MAC). From Fig. 6, it is obvious that there is another signal from drain of M4 to bulk terminal of M5. Indeed, M5 has 2 amplified signal as input, one from MAC drain and another from MA drain. As mentioned in part 2, this technique increases the effective transconductance with  $g_{mb}$  factor which could change some parameters of whole circuit. The major change belongs to output impedance and also other parameter have little improvement. Analysis and mathematical calculations are described in next subsection.

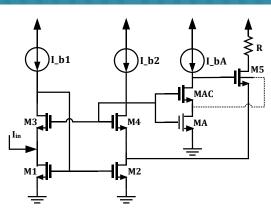

#### B. Output impedance

One of the most significant factors of each current mirror is its high output impedance and low input impedance (Ramirez et al, 2005) (Garimella et al, 2005) (Cong and Geiger, 2000). Using the bulk driven technique in final stage transistor, M5, increases output impedance while other parameters do not modify expressively. According to the circuit shown in Fig. 6, the output impedance of the current mirror with applied technique is equal to:

$$V_{out} = V_{ds} + V_{d2}$$

$$V_{ds5} = (I_{out} - g_{m5}V_{gs5} - g_{mb5}V_{bs5})r_{o5}$$

$$V_{gs5} = -(1 + A)V_{d2}$$

$$A = g_{mA}(\frac{g_{m,AC}}{g_{ds,A}g_{ds,AC} + g_{ds,bA}g_{m,AC}}||r_{ob,A})$$

$$V_{bs5} = V_{dmA} - V_{d2}$$

$$V_{d,mA} = -V_{d2} \times g_{mA} \times R_{o,mA}$$

That  $R_{o,mA}$  is equal to:

$R_{o,mA} = r_{ds,mA} || \frac{r_{obA} + r_{ds,mAC}}{1 + g_{m,AC} r_{ds,AC}}$ Thus:

$V_{bs5} = -V_{d2}(1 + g_{mA}R_{o,mA})$

تركية – استانيول

۲۴ اسفند ۱۳۹۴

Istanbul-Turkey 14 March 2016

$$V_{ds5} = r_{o5}I_{out} + g_{m5}r_{o5}(1+A)V_{d2} + g_{mb5}V_{d2}(1+g_{mA}R_{o,mA})$$

$$V_{d2} = (r_{ob2}||r_{o2})(I_{out} - g_{m2}V_{d2})$$

$$V_{d3} = -g_{m3}(r_{ob1}||g_{m3}r_{o3}r_{o1})(V_{d2} - V_{d1})$$

$$V_{d1} = -\frac{g_{m1}}{g_{m3}}V_{d3}$$

$$V_{d3} = -g_{m3} (r_{ob1} || g_{m3} r_{o3} r_{o1}) (V_{d2} + \frac{g_{m1}}{g_{m3}} V_{d3})$$

$$V_{d3} = -\frac{g_{m3}(r_{ob1}||g_{m3}r_{o3}r_{o1})}{1 + g_{m1}(r_{ob1}||g_{m3}r_{o3}r_{o1})} V_{d2}$$

$$V_{d2} = \frac{(r_{ob}||r_{o2})I_{out}}{1 - \frac{g_{m2}g_{m3}(r_{ob2}||r_{o2})(r_{ob1}||g_{m3}r_{o3}r_{o1})}{1 + g_{m1}(r_{ob1}||g_{m3}r_{o3}r_{o1})}$$

$$V_{out} = I_{out}r_{o5} + V_{d2} \Big[ 1 + g_{m5}(1+A)r_{o5} + g_{mb5}r_{o5} \Big( 1 + g_{mA}R_{o,mA} \Big) \Big]$$

$$R_{out} = r_{o5} + \frac{(r_{ob2}||r_{o2})}{1 - \frac{g_{m2}g_{m3}R_2R_3}{1 + g_{m1}R_3}} [1 + g_{m5}(1+A)r_{o5} + g_{mb5}r_{o5}(1 + g_{mA}R_{omA})]$$

(4)

Approximate calculation of the output impedance of the circuit shown in Fig. 5 is:

$$R_{out} = r_{o5} + \frac{(r_{ob2}||r_{o2})(g_{m5}(1+A)r_{o5})}{1 - \frac{g_{m2}g_{m3}(r_{ob2}||r_{o2})}{1 + g_{m1}}}$$

(5)

While the exact calculation of the output impedance of circuit shown in Fig. 5 is equal to:

$$R_{out} = r_{o5} + \frac{(r_{ob2}||r_{o2})}{1 - \frac{g_{m2}g_{m3}R_2R_3}{1 + g_{m1}R_3}} \left(1 + g_{m5}(1+A)r_{o5}\right)$$

(6)

In all calculations, R2 and R3 are equal to:

$$R_2 = r_{ob2} || r_{o2} \tag{7}$$

$$R_3 = r_{ob1} ||g_{m3} r_{o3} r_{o1}$$

(8)

Comparison of (6) and (4) shows that the applied bulk driven technique increases the output impedance of current mirror with following factor:

$$(r_{ob2}||r_{o2})/(1 - \frac{g_{m2}g_{m3}R_2R_3}{1 + g_{m1}R_3})[g_{mb5}r_{o5}(1 + g_{mA}R_{omA})]$$

Also, comparison with other works shows that this idea has a very high output resistance for an LVLP current mirror.

#### C. Input impedance

It is good to have low input impedance for each current mirror. As mentioned, applied signal path to bulk of M5 does not significant effects on other parameters except output resistance and current transfer error. One of these parameters is input resistance that following steps show the input impedance calculation of proposed idea. Input resistance of Fig. 6 is equal to:

$$I_{in} = \left[ \left( g_{m1} + \frac{g_{m3}g_{m1}}{(g_{m5} + g_{mb5})(1+A)} \right) \times K + G \right] V_{in}$$

(9)

Thus input resistor:

تركيه – استانبول

۲۴ اسفند ۱۳۹۴

Istanbul-Turkey

T 7

/ 14 March 2016

Fig 7. Small signal view of current mirror with proposed idea

$$R_{\rm in} = \frac{V_{in}}{I_{in}} = \frac{1}{\left[ \left( g_{m1} + \frac{g_{m3}g_{m1}}{(g_{m5} + g_{mb5})(1+A)} \right) \times K + G \right]}$$

(10)

K and G in above equation are:

$$K = \frac{g_{m3}^2(g_{m5} + g_{mb5})(1+A)}{(g_{m5} + g_{mb5})g_{ds1}g_{ds3}(1+A) - g_{m1}g_{m3}^2}$$

$$G = g_{ds1} + g_{m3} + g_{ds3}$$

On the other hand, input resistance calculation of the circuit shown in Fig. 5 is reported (Azhari et al, 2011):

$$R_{in} = \frac{g_{m1}g_{ds3}g_{ds1}(A+1) - g_{m1}g_{m3}^2}{g_{m1}g_{m3}^2g_{m5}(1+A)}$$

(11)

Nevertheless, precise input resistance calculation of the circuit shown in Fig. 5 results:

$$R_{\rm in} = \frac{1}{\left(g_{m1} + \frac{g_{m3}g_{m1}}{g_{m5}(1+A)}\right) \left(\frac{g_{m3}^2g_{m5}(1+A)}{g_{m5}g_{ds1}g_{ds3}(1+A) - g_{m1}g_{m3}^2}\right) + G}$$

(12)

Consequently, comparison of (10) and (12) shows that proposed idea has no change in the input resistance. The new circuit has low input impedance subsequently.

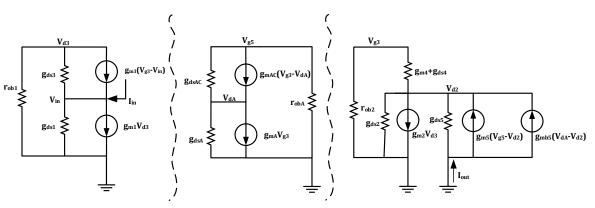

#### D. Current transfer analysis

Current transfer accuracy in current mirror design is one of the most significant factors. The best current mirror is one that has less current transfer error. For evaluating and analysis of this factor, following equations are calculated through small signal model of circuit as shown in Fig. 7.

$$\begin{split} I_{in} &= V_{d3}(g_{m1} - g_{ds3}) + V_{in}(g_{ds1} + g_{m3} + g_{ds3}) - g_{m3}V_{g3} \\ V_{g3} &= \frac{I_{out}}{(g_{mb5} + g_{m5})(1 + g_{mA}r_{obA})} \end{split}$$

It is clear from comparison of the calculated  $\lambda$  in (13) and the circuit shown in Fig. 5 (Azhari et al, 2011) which this idea has better accuracy in current transfer rather than the current mirror circuit shown in Fig. 5. The reason is that, according to (13), when the effective gm of the transistor M5 increases, the deduction  $\frac{g_{ds1}}{(g_{m5}+g_{mb5})g_{mA}r_{obA}}$  becomes lower and will be less effective when sum with 1, therefore the value of  $\lambda$  will be closer to the ideal one.

#### Simulation results

LVLP current mirror circuit with applied technique is simulated in 0.18  $\mu$ m technology. To compare the results of improved current mirror with proposed circuit in (Azhari et al, 2011), power supply is set 1V and load resistance equal to  $3k\Omega$ . As well as, to evaluate the effect of improvement, all values of the circuit parameters are the same as to the values reported in (Azhari et al, 2011), just new signal path is added to bulk of M5. The simulation results of LVLP current mirror with and without applied technique are reported in the following.

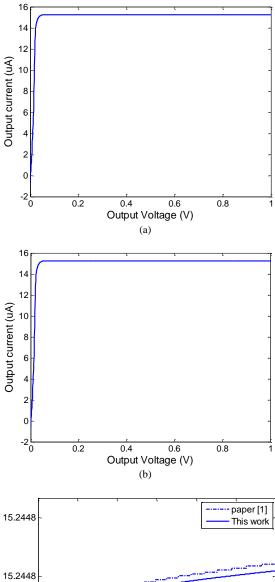

To find the output resistance of current mirror from simulation graphs, reverse slope of the output current versus output voltage curve, is measured. Fig. 8 (a) and (b) show the output current versus output voltage of current mirror with and without applied technique, respectively. As shown in Fig. 8 (a), the improved circuit exhibits extremely high output resistance of 39.5 G $\Omega$ , which results more than 5G $\Omega$  improvement Compare with the output resistor of current mirror without applied technique is reported in (Azhari et al, 2011), (Fig. 8 (c)).

According to the results of simulation, minimum output voltage of both current mirrors, with and without applied technique, are 0.55 mV and show that dynamic range are same in both case.

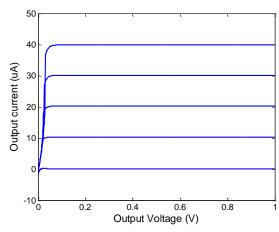

Fig. 9 belongs to output current versus output voltage for input current value of: 0 uA, 10 uA, 20 uA, 30 uA, and 40 uA. The results proved that proposed idea has no negative effect on circuit performances. As it is obvious from simulation results, proposed idea has the higher output resistance rather than other same reported works.

#### A convernation **BNAL CONFERENCE ON** ENCE RE d CHN D 0) Δ Ξ C

14 March 2016

Istanbul-Turkey

دومین کنفرانی بین المللے یزوهنتر درعلوم و تکنولوز ہے ترکیه - استانبول ۲۴ اسفند ۱۳۹۴

15.2448 Output current (uA) 15.2448 15.2448 15.2448 0.2 0.3 0.4 0.5 0.6 0.7 0.8 Output Voltage (V)

Fig 8.  $I_{out}$  versus  $V_{out}$  to find  $g_{out}(R_{out}^{-1})$  for Current mirror circuit a) with b) without applied technique (Azhari et al, 2011), c) compare  $g_{out}$  of (a) and (b).

(c)

Istanbul-Turkey 1

14 March 2016

Fig 9. Output current versus output voltage for different input current of current mirror circuit with applied technique.

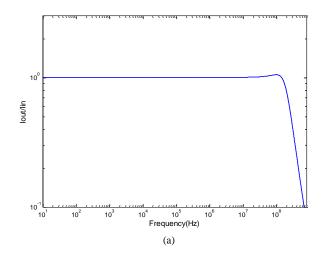

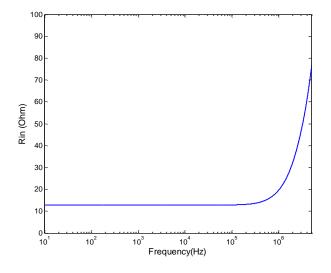

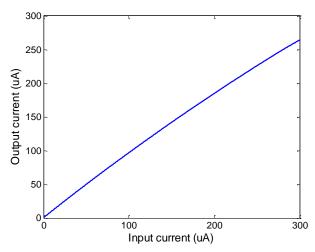

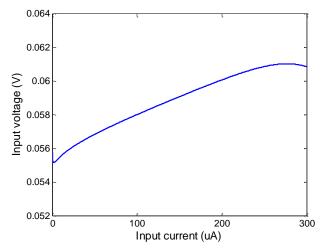

The frequency response of both current mirrors are illustrated in Fig. 10. As expected, not only did the applied technique have no negative impact on bandwidth, but also it made a little enhancement in circuit bandwidth. The bandwidth is achieved 216 MHz in this work. Input resistance versus frequency is depicted in Fig. 11. Result of simulation shows that input resistor is equal to 12.8  $\Omega$ . As expected, applied technique has no considerable effect on input resistance. The output current and input voltage versus input current are shown in Figs. 12 and 13, respectively. It is clear that current gain and input voltage are same in both case and has no considerable differences.

Comparative results of two current mirrors, with applied technique proposed in this work and without applied technique (Azhari et al, 2011), are summarized in Table 1. It should be noted that the difference between these two works is just extra signal path to bulk of M5, and all other things are completely same. As a result, the proof of which are independent of the parameters values and circuit design, using the applied bulk driven technique improve the current mirror performances.

Fig 10. Current mirror frequency response a) with b) without applied technique (Azhari et al, 2011)

Fig 11. Input resistor of current mirror with applied technique

| reference            | (Azhari et al<br>2011) | (Raj et al<br>2015) | (Raj et al<br>2014) | (Bhawna et al<br>2014) | This work |

|----------------------|------------------------|---------------------|---------------------|------------------------|-----------|

| I <sub>in</sub> (uA) | 15                     | 0-250               | 0-700               | 0-280uA                | 15        |

| I <sub>b</sub> (mA)  | 5                      | NA                  | 65                  | NA                     | 5         |

| Vin,min (V)          | 0.058                  | NA                  | NA                  | NA                     | 0.058     |

| Vout,min (V)         | 0.055                  | NA                  | NA                  | NA                     | 0.055     |

| $R_{in}(\Omega)$     | 13.3                   | 240                 | 160                 | 2730                   | 12.8      |

| Rout (Ω)             | 34.3 G                 | 19.5G               | 8.55G               | 578K                   | 39.5 G    |

| BW (MHz)             | 210                    | 285                 | 4000                | 132                    | 216       |

| P (uW)               | 42.5                   | 349                 | 840                 | NA                     | 42.5      |

| V supply (V)         | 1                      | 0.2                 | 0.5                 | ±0.5                   | 1         |

| Technology           | 0.18 um                | 0.18 um             | 0.35 um             | 0.25 um                | 0.18 um   |

### ومين كنفرانى يين المللم يتزوهنتر درعلوم وتكنولوت س

Istanbul-Turkey

CH

Ξ

D

Turkey 14 March 2016

**CONFERENCE ON**

0][

dI

Fig 12. Output current versus input current for Current mirror circuit with applied technique.

Fig 13. Input voltage versus input current for Current mirror circuit with applied technique.

#### Conclusion

This paper presents an LVLP current mirror with very high output resistance which is based on bulk driven technique. By using of an extra signal path to the bulk terminal of output transistor, the performance of current mirror, especially the output resistance, enhanced significantly. Simulation results show a significant output resistance improvement, which indicates more than 5G $\Omega$  improvement in compare with output resistor of the current mirror without applied technique. Also, this paper proved that appropriate use of bulk driven technique, independent of the parameters values and circuit design, is a suitable way to improve current mirror performance.

Istanbul-Turkey 14 March 2016

#### References

Angulo Ramirez, Sawant, Martín López, Carvajal (2005). Compact implementation of high-performance CMOS current mirror", Electronics Letters, Vol. 41(10), pp. 570 – 572.

Azhari Seyed Javad, Faraji Baghtash Hasan, Monfaredi Khalil. (2011). A novel ultra-high compliance, high output impedance low power very accurate high performance current mirro. Microelectronics Journal. Vol. 42.432–439.

Aggarwal, Bhawna, Maneesha Gupta, and A. K. Gupta, (2012) "Analysis of low voltage bulk-driven self-biased high swing cascode current mirror", Microelectronics Journal, vol. 44, no. 3, pp. 225-235.

Bdiri Gabbouj Houda, Hassen Nejib, Bsebes Kamel. (2008). Comparative study and design of new low voltage high performance current mirrors. Design and Technology of Integrated Systems in Nanoscale Era. Proceedings of the 3rd International Conf. on IEEE.pp.1-6.

Cheng Ku Hsing, Chen Chi, Chung Chun-fu. (2001). Accurate current mirror with high output impedance. The 8th IEEE International Conference on Electronics, Circuits and Systems, Vol. 2. pp. 565 – 568.

Cong Y, Geiger R.L, (2000). Cascode current mirrors with low input, output and supply voltage requirements. Proceedings of the 43rd MWSCAS, Lansing MI, pp. 490–493.

Ebrahimi Ali, Bastan Yasin, Ebrahimi Emad, Shamsi Hossein. (2015). Exploiting crosscoupled and body-driven techniques for noise cancellation of an inductor-less wideband LNA, International Journal of Electronics and Communications, Vol. 69(4), pp.708–714.

Garimella Annajirao. Angulo Ramirez, Martín López, Carvajal. (2005). Low-voltage high performance compact all cascode CMOS current mirror. Electronics Letters, Vol. 41(25), pp. 1359–1360

Haga Y, Zare-Hoseini H, Berkovi L. (2005). Design of a 0.8 Volt Fully Differential CMOS OTA Using the Bulk Driven Technique. IEEE International Symposium on Circuits and Systems. ISCAS Vol. 1, pp. 220 – 223.

Murphy Marc.W, El-Masry Ezz. Elshurafa Amro.M. (2006). A high compliance input and output regulated body-driven current mirror for deep-submicron CMOS. Proceedings of the ICM'06 International Conference on IEEE, Microelectronics, pp. 13–16.

Raj, Nikhil, Ashutosh Kumar Singh, and Anil Kumar Gupta, (2015), "Low Voltage High Output Impedance Bulk-Driven Quasi-Floating Gate Self-Biased High-Swing Cascode Current Mirror." Circuits, Systems, and Signal Processing: 1-21.

Raj, Nikhil, Ashutosh Kumar Singh, and Anil Kumar Gupta, (2014), "Low power high output impedance high bandwidth QFGMOS current mirror." Microelectronics Journal 45.8, 1132-1142.

Istanbul-Turkey 14 March 2016

IN SCIENCE

C

**ONAL CONFERENCE ON**

TECHNOL

AND

Rajput S. S, Jamuar S. S. (2002). Low Voltage Analog Circuit Design Techniques. Circuits and Systems Magazine, IEEE, Vol. 2(1), pp. 24-42.

Razavi Behzad. (2007). Fundamentals of Microelectronics Razavi. Willy Library

Sawant Milind Subhash, et al. (2005), New compact implementation of a very high performance CMOS current mirror, in: Proceedings of the 48th Midwest Symposium on IEEE, Circuits and Systems, vol. 1, pp. 840–842.

Sharma Susheel, Rajput S, Mangotra L.K, Jamuar S.S. (2006). FGMOS current mirror: behaviour and bandwidth enhancement. Analog Integrated Circuits and Signal Processing, pp. 281–286.

Volta Su, Inc. (2009), Body Effect and Body Biasing. Los Gatos, California, 95032-1832 USA.

Yani Li, Yintang Yong, Zhangming Zhu. (2010). A Novel Low-voltage Low-power Bulkdriven Cascade Current Mirror. 3rd International Conference on Advanced Computer Theory and Engineering (ICACTE).

Zhu Zhangming, Mo Jianbin, Yang Yintang. (2008). A Low Voltage Bulk-driving PMOS Cascode Current Mirror. 9th International Conference on Solid-State and Integrated-Circuit Technology, pp.2008-2011.